이 번역 페이지는 최신 내용을 담고 있지 않습니다. 최신 내용을 영문으로 보려면 여기를 클릭하십시오.

외란 보상

선형 시스템의 외란과 알 수 없는 동특성 추정 및 보상

입력과 출력을 기반으로 플랜트의 상태와 외란을 추정할 수 있는 추정 기법을 사용합니다.

블록

| Active Disturbance Rejection Control | 동특성과 외란을 알 수 없는 플랜트에 대한 제어기 설계 (R2022b 이후) |

| Extended State Observer | Estimate states and disturbances of a system (R2024a 이후) |

| Disturbance Compensator | Modify control actions to compensate for unknown dynamics and disturbances (R2024a 이후) |

| Ultra Local Model | Estimate nonlinear plant as single or double integrator systems with an affine term that captures unknown dynamics and disturbances (R2025a 이후) |

도움말 항목

능동 외란 제거 제어(ADRC)

- 능동 외란 제거 제어(ADRC)

동특성과 외란을 알 수 없는 플랜트에 대한 외란 제거 제어기를 설계합니다. - Design Active Disturbance Rejection Control for Water-Tank System

Design ADRC for a water-tank model and compare performance against a gain-scheduled PID controller. - Design ADRC for Multi-Input Multi-Output Plant

Design ADRC for a pilot-scale distillation column MIMO model and compare performance against a model predictive controller. (R2023b 이후)

외란 보상

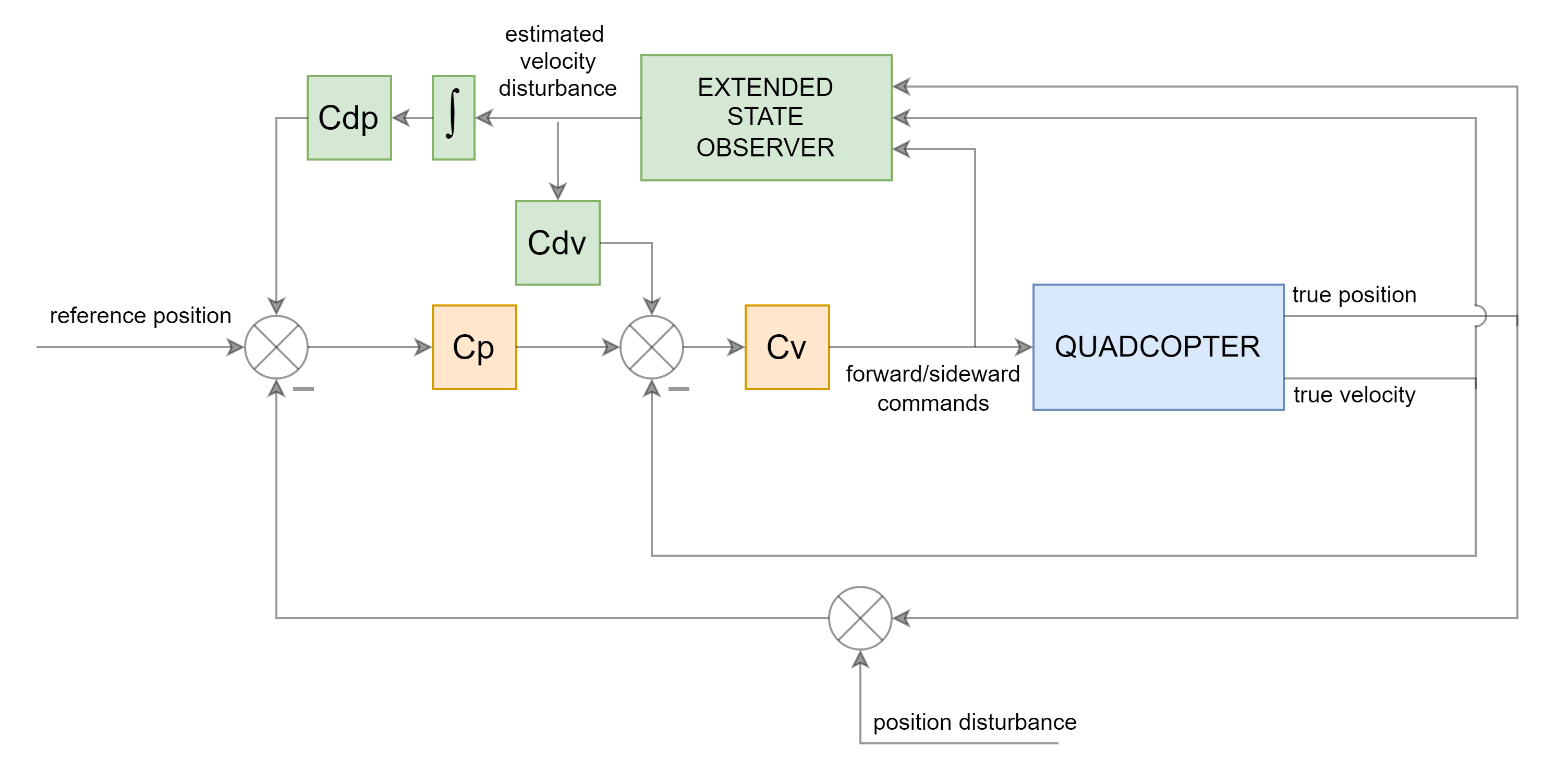

- Control Design and Disturbance Compensation Using Extended State Observers

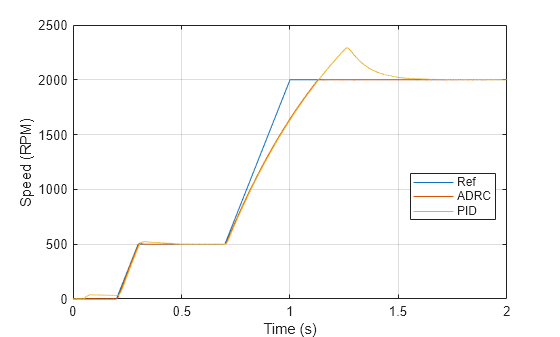

Estimate and compensate for disturbances and unknown dynamics in linear time-invariant or linear time-varying systems. (R2024a 이후) - Apply Extended State Observer for Reference Tracking of DC Motor

Improve the disturbance rejection performance of a PID controller using the Extended State Observer block. (R2024a 이후) - Compensate for Disturbances in Spring-Mass-Damper System

Compensate for disturbances in a spring-mass-damper system using the Disturbance Compensator block. (R2024a 이후)

Ultra-Local Model

- Ultra-Local Model for Disturbance Estimation and Compensation

Estimate disturbances and unmodeled dynamics using ultra-local model. - Ultra-Local Model for System Identification and Output Prediction

Use the Ultra-Local Model block for system identification and output prediction. - Intelligent PID Using Ultra Local Model for Ball on Beam Balance

Implement model-free intelligent PID control technique using ultra-local model.

코드 생성

- Deploy Controller for SEPIC Converter for PIL Testing

Set up processor in the loop (PIL) testing and profiling of an active disturbance rejection controller for a SEPIC converter. (R2024b 이후)