Deploy IP Core on Custom Hardware

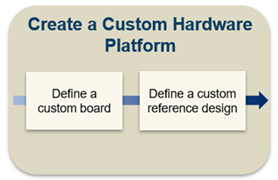

HDL Coder™ supports a limited number of pre-existing target platforms. For rapid prototyping, a pre-existing board works, but for production, a custom platform is typically required. Create a custom platform to integrate the IP core into a standalone FPGA board or SoC platform with Xilinx® Vivado® IP Integrator or Intel® Qsys.

You can create your own custom reference design in MATLAB® and use HDL Coder to integrate the IP core into your reference design.

For more details on the workflow, see Targeting FPGA & SoC Hardware Overview.

Classes

hdlcoder.Board | Board registration object that describes SoC custom board |

hdlcoder.ReferenceDesign | Reference design registration object that describes SoC reference design |

Functions

Topics

Board and Reference Design

- Board and Reference Design Registration System

System for defining and registering boards and reference designs. - Register a Custom Board

Define the interface and attributes of a custom SoC board. After defining the board, you can target it using the IP Core Generation Workflow in the HDL Workflow Advisor. - Register a Custom Reference Design

Define the interface and attributes of a custom SoC reference design. After defining and registering the reference design, you can target it using the IP Core Generation Workflow in the HDL Workflow Advisor. - Define Custom Parameters and Callback Functions for Custom Reference Design

Learn how to define custom parameters and custom callback functions for your custom reference design. - Customize Reference Design Dynamically Based on Reference Design Parameters

Learn how to customize the reference design dynamically by using theCustomizeReferenceDesignFcnmethod. - Define and Add IP Repository to Custom Reference Design

Learn how you can create an IP repository and add the IP modules in the repository to your custom reference design. - Define Multiple AXI Master Interfaces in Reference Designs to Access DUT AXI4 Subordinate Interface

Learn how you can specify multiple AXI Master interfaces in the custom reference design to access HDL DUT IP AXI4 subordinate interface. - Generate HDL IP Core with Multiple AXI4-Stream and AXI4 Master Interfaces

Learn how you can map your DUT ports to multiple AXI4-Stream, AXI4-Stream Video, and AXI4 Master interfaces. - Use Callback Functions in Custom Reference Design

This example illustrates how to customize the reference design dynamically by using a callback function based on the reference design parameter options. - IP Caching for Faster Reference Design Synthesis

Use IP caching to speed up reference design synthesis time by using an out-of-context workflow. - Generate Device Tree for IP Core

Generate device tree files that include the HDL Coder generated IP core. - Export Custom Reference Design from SoC Model (SoC Blockset)

Use thesocExportReferenceDesignfunction to export a custom reference design from an SoC Blockset™ model.

Specific Hardware Platforms

- Define Custom Board and Reference Design for AMD Workflow

This example shows how to define and register a custom board and custom reference design in the Zynq® workflow. - Build Custom Linux Image for IP Core

This example shows how to set up a build environment and create a Linux® image for an IP core for the Digilent Zybo™ Z7-10 Zynq® board by using the MathWorks® build system. - Define Custom Board and Reference Design for Intel Workflow

This example shows how to define and register a custom board and reference design in the HDL Coder™ Intel® SoC workflow. - Define Custom Board and Reference Design for Microchip Workflow

This example shows how to define and register a custom board and reference design for a blinking LED model in the Microchip workflow of the HDL Workflow Advisor. - Define Custom Board and Reference Design for Pure Microchip FPGA Workflow

Define and register Pure FPGA boards and reference designs for an LED blinking model using Microchip Polarfire® in the HDL Workflow Advisor. - Define Custom Board and Reference Design for Zynq Ultrascale+ MPSoC Workflow

This example shows how to define and register a custom board and reference design for the Zynq® workflow using a Xilinx® Zynq UltraScale+™ MPSoC ZCU104 evaluation kit. - Build Custom Reference Design to Interface with Peripheral Chip

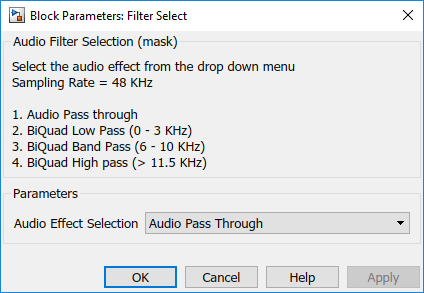

This example shows how to build a reference design to run an audio algorithm and access audio input and output on a Zynq® board. - Authoring a Reference Design for Audio System on a ZYBO Board

This example shows how to build a reference design to run an audio algorithm and access audio input and output on ZYBO™ Z7-10 board. - Author Audio System Reference Design for Basic Intel Evaluation Board

This example shows how to build a reference design to run an audio algorithm and access audio input and output on an Intel® Arrrow® SoC board. - Build Linux Image for Microchip PolarFire SoC by Using Yocto Build System

This example shows how to build a Linux® image for the Microchip Polarfire® SoC (PFSoC) Icicle kit. - Define Custom Board and Reference Design for AMD Kria KR260 Robotics Kit

Set up a custom KR260 board and reference design to enable IP core generation and control LEDs. (Since R2026a) - Define Custom Board and Reference Design for AMD Kria KV260 Vision AI Starter Kit

Set up a custom KV260 board and reference design to enable IP core generation and control LEDs. (Since R2026a)

Related Information

Troubleshooting

Resolve Timing Failures in IP Core Generation and Simulink Real-Time FPGA I/O Workflows

Resolve timing failures in Build FPGA Bitstream step of IP Core Generation Workflow or Simulink Real-Time FPGA I/O Workflow for Vivado-Based Boards.