이 번역 페이지는 최신 내용을 담고 있지 않습니다. 최신 내용을 영문으로 보려면 여기를 클릭하십시오.

Signal Conversion

신호 값을 변경하지 않고 신호를 새 유형으로 변환

라이브러리:

Simulink /

Signal Attributes

HDL Coder /

Signal Attributes

Signal Conversion 블록의 대체 구성:

Signal Copy | To Virtual Bus | To Nonvirtual Bus

설명

Signal Conversion 블록은 신호를 한 유형에서 다른 유형으로 변환합니다. 수행할 변환 유형을 선택하려면 출력 파라미터를 사용하거나 아래와 같은 사전 구성된 Signal Conversion 블록 중 하나를 사용하십시오.

Signal Copy 블록

To Virtual Bus 블록

To Nonvirtual Bus 블록

예제

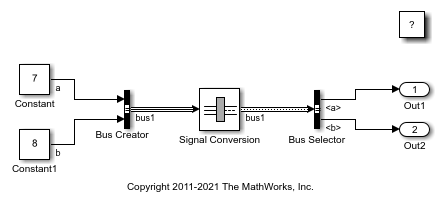

Signal Conversion 블록을 사용하여 버스의 연속 복사본을 만듭니다.

Bus Creator 블록은 Signal Conversion 블록에 입력되는 비가상 버스를 만듭니다. 출력 파라미터를 Signal copy로 설정하면, Signal Conversion 블록은 해당 입력 버스의 또 다른 연속 복사본을 만듭니다.

Signal Conversion 블록을 사용하여 가상 버스를 비가상 버스로 변환합니다.

Bus Creator 블록은 Signal Conversion 블록에 입력되는 가상 버스를 만듭니다. 가상 버스를 비가상 버스로 변환하려면, Signal Conversion 블록의 출력 파라미터를 Nonvirtual bus로 설정하고 데이터형 파라미터를 Simulink.Bus 객체로 설정합니다. 지정된 Bus 객체는 Bus Creator 블록의 버스 계층 구조와 일치합니다. Signal Conversion 블록의 비가상 버스 출력은 Bus Selector 블록에 대한 입력이 됩니다.

Signal Conversion 블록을 사용하여 비가상 버스를 가상 버스로 변환합니다.

Bus Creator 블록은 Signal Conversion 블록에 입력되는 비가상 버스를 만듭니다. 비가상 버스를 가상 버스로 변환하려면 Signal Conversion 블록의 출력 파라미터를 Virtual bus로 설정합니다. Signal Conversion 블록의 가상 버스 출력은 Bus Selector 블록에 대한 입력이 됩니다.

Signal Conversion 블록을 사용하여 다중화 신호를 벡터로 변환합니다.

Mux 블록은 Signal Conversion 블록에 입력되는 다중화 신호를 만듭니다. 다중화 신호를 벡터로 변환하려면 Signal Conversion 블록의 출력 파라미터를 Signal copy로 설정합니다. Signal Conversion 블록의 벡터 출력은 Display 블록에 대한 입력이 됩니다.

포트

입력

블록이 다른 유형으로 변환할 입력 신호로, 스칼라, 벡터, 행렬, 배열 또는 버스일 수 있습니다.

데이터형: single | double | half | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | string | Boolean | fixed point | enumerated | bus | image

출력

출력 신호는 입력 신호를 지정된 유형으로 변환한 신호입니다.

데이터형: single | double | half | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point | enumerated | bus | image

파라미터

블록 파라미터를 대화형 방식으로 편집하려면 속성 인스펙터를 사용합니다. Simulink® 툴스트립의 시뮬레이션 탭에 있는 준비 갤러리에서 속성 인스펙터를 선택하십시오.

수행할 변환의 유형을 지정하십시오.

신호 복사— 입력 신호의 연속 복사본을 만듭니다. 이 값은 Signal Conversion 블록 및 Signal Copy 블록의 디폴트 값입니다.가상 버스— 비가상 버스를 가상 버스로 변환합니다. 이 값은 To Virtual Bus 블록의 디폴트 값입니다.비가상 버스— 가상 버스를 비가상 버스로 변환합니다. 이 값은 To Nonvirtual Bus 블록의 디폴트 값입니다.

신호 복사 옵션의 경우, 입력의 유형에 따라 블록이 복사본을 만드는 방법이 결정됩니다.

예를 들어, 블록이 다중화 신호를 수신하고 있고 이 신호의 요소가 메모리에서 불연속적인 영역을 차지하고 있다고 가정해 보겠습니다. 변환은 다중화 신호의 요소를 위해 연속적인 메모리 영역을 할당하며, 각 시간 스텝마다 블록 입력이 나타내는 불연속 영역의 값을 블록 출력이 나타내는 연속 영역으로 복사합니다. 출력은 메모리의 연속 영역을 차지하는 요소를 갖는 벡터입니다.

사용하는 변환 유형은 모델링 목표에 따라 달라집니다.

| 모델링 목표 | 옵션 |

|---|---|

다중화 신호에 대해 생성되는 코드를 줄입니다. Simulink Coder™와 관련된 예제는 Generate Reentrant Code from Subsystems (Simulink Coder) 항목을 참조하십시오. | 신호 복사 |

상수 샘플 시간을 갖는 블록을 Enabled Subsystem의 출력 포트에 연결합니다. | 신호 복사 |

비가상 버스를 가상 버스로 변환하여 메모리를 절약합니다. | 가상 버스 |

비가상 버스를 필요로 하는 모델링 구문에 가상 버스를 전달합니다. | 비가상 버스 |

버스로 구성된 배열의 복사본을 만듭니다. 이 블록은 버스로 구성된 배열을 비가상 버스 또는 가상 버스로 변환할 수 없습니다. 버스로 구성된 배열에서 버스를 추출하려면 Selector 블록을 사용하십시오. | 신호 복사 |

프로그래밍 방식의 사용법

프로그래밍 방식으로 블록 파라미터 값을 설정하려면 set_param 함수를 사용하십시오.

| 파라미터: | ConversionOutput |

| 값: | 'Signal copy' (디폴트 값) | 'Virtual bus' | 'Nonvirtual bus' |

예: set_param(gcb,'ConversionOutput','Virtual bus')

이 블록이 생성하는 비가상 버스의 출력 데이터형을 지정하십시오.

Inherit: auto— 업스트림 블록에서 데이터형을 상속합니다. 예를 들어, 업스트림 Bus Creator 블록에서Simulink.Bus객체 데이터형을 상속합니다.Bus: <object name>또는<data type expression>— 입력 버스의 계층 구조와 일치하는Simulink.Bus객체를 지정합니다. 업스트림 Bus Creator 블록이 버스 객체를 지정하는 경우 동일한 버스 객체를 지정합니다.

데이터형 도우미를 사용하면 데이터 특성을 쉽게 설정할 수 있습니다. 데이터형 도우미를 사용하려면  을 클릭하십시오. 자세한 내용은 Specify Data Types Using Data Type Assistant 항목을 참조하십시오.

을 클릭하십시오. 자세한 내용은 Specify Data Types Using Data Type Assistant 항목을 참조하십시오.

종속성

이 파라미터를 활성화하려면 출력을 비가상 버스로 설정하십시오.

프로그래밍 방식의 사용법

프로그래밍 방식으로 블록 파라미터 값을 설정하려면 set_param 함수를 사용하십시오.

| 파라미터: | OutDataTypeStr |

| 값: | 'Inherit: auto' (디폴트 값) | 'Bus: <object name>' | '<data type expression>' |

예: set_param(gcb,'OutDataTypeStr','Bus: myBusObj')

입력 신호의 요소가 메모리에서 연속적인 영역을 차지하는 경우, 기본적으로 소프트웨어는 최적화의 일환으로 컴파일된 모델에서 이 블록을 제거합니다. 자세한 내용은 Block reduction 항목을 참조하십시오.

컴파일된 모델에서 이 블록이 제거되는 것을 방지하려면 이 파라미터를 선택하십시오.

이 파라미터의 변경 사항은 다음에 모델을 컴파일할 때 적용됩니다.

종속성

이 파라미터를 활성화하려면 출력을 신호 복사로 설정하십시오.

프로그래밍 방식의 사용법

프로그래밍 방식으로 블록 파라미터 값을 설정하려면 set_param 함수를 사용하십시오.

| 파라미터: | OverrideOpt |

| 값: | 'off' (디폴트 값) | 'on' |

예: set_param(gcb,'OverrideOpt','on')

블록 특성

데이터형 |

|

직접 피드스루 |

|

다차원 신호 |

|

가변 크기 신호 |

|

영점교차 검출 |

|

대체 구성

Signal Copy 블록은 Signal Conversion 블록과 이름만 다릅니다.

라이브러리:

Simulink /

Quick Insert /

Signal Attributes

To Virtual Bus 블록은 출력을 가상 버스로 설정합니다.

라이브러리:

Simulink /

Quick Insert /

Signal Attributes

To Nonvirtual Bus 블록은 출력을 비가상 버스로 설정합니다.

라이브러리:

Simulink /

Quick Insert /

Signal Attributes

확장 기능

C/C++ 코드 생성

Simulink® Coder™를 사용하여 C 코드나 C++ 코드를 생성할 수 있습니다.

HDL Coder™는 HDL 구현과 합성된 논리에 영향을 주는 추가 구성 옵션을 제공합니다.

이 블록은 패스스루(pass-through) 구현을 갖습니다.

| ConstrainedOutputPipeline | 기존 지연을 설계 내부로 이동하여 출력에 배치하는 레지스터 개수입니다. 분산된 파이프라이닝은 이러한 레지스터를 다시 분산하지 않습니다. 디폴트 값은 |

| InputPipeline | 생성된 코드에 삽입할 입력 파이프라인 단계의 개수입니다. 분산 파이프라이닝과 제약이 있는 출력 파이프라이닝은 이러한 레지스터를 이동할 수 있습니다. 디폴트 값은 |

| OutputPipeline | 생성된 코드에 삽입할 출력 파이프라인 단계의 개수입니다. 분산 파이프라이닝과 제약이 있는 출력 파이프라이닝은 이러한 레지스터를 이동할 수 있습니다. 디폴트 값은 |

이 블록은 복소 신호를 위한 코드 생성을 지원합니다.

PLC 코드 생성

Simulink® PLC Coder™를 사용하여 Structured Text 코드를 생성할 수 있습니다.

고정소수점 변환

Fixed-Point Designer™를 사용하여 고정소수점 시스템을 설계하고 시뮬레이션할 수 있습니다.

버전 내역

R2006a 이전에 개발됨

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

웹사이트 선택

번역된 콘텐츠를 보고 지역별 이벤트와 혜택을 살펴보려면 웹사이트를 선택하십시오. 현재 계신 지역에 따라 다음 웹사이트를 권장합니다:

또한 다음 목록에서 웹사이트를 선택하실 수도 있습니다.

사이트 성능 최적화 방법

최고의 사이트 성능을 위해 중국 사이트(중국어 또는 영어)를 선택하십시오. 현재 계신 지역에서는 다른 국가의 MathWorks 사이트 방문이 최적화되지 않았습니다.

미주

- América Latina (Español)

- Canada (English)

- United States (English)

유럽

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)