이 번역 페이지는 최신 내용을 담고 있지 않습니다. 최신 내용을 영문으로 보려면 여기를 클릭하십시오.

Enabled Subsystem

외부 입력으로 실행이 활성화되는 서브시스템

라이브러리:

Simulink /

Ports & Subsystems

HDL Coder /

Ports & Subsystems

설명

Enabled Subsystem 블록은 외부 신호를 기반으로 이 신호가 양수 값을 가질 때 실행되는Subsystem 블록입니다. Enabled Subsystem은 Enable 포트의 외부 신호가 음수에서 양수 방향으로 0을 교차할 때 실행됩니다.

Enabled Subsystem 블록은 Subsystem 블록 안에 Enable 블록을 배치하여 구성됩니다. Enabled Subsystem의 실행은 Enabled Subsystem 블록의 Enable 포트에 의해 제어됩니다.

Enabled Subsystem 블록을 사용하여 다음을 모델링합니다.

서브시스템 내부 블록의 실행이 불연속적임. 예를 들어, Counters Using Conditionally Executed Subsystems의 카운터 회로는 서브시스템이 활성화되어 있는 동안 증가하고 서브시스템이 비활성화되었을 때 그 출력을 유지합니다.

서브시스템이 Enable 포트에서 양의 제어 신호를 받을 때 실행되는 복수의 Enabled Subsystem. Enabled Subsystem을 사용하여 제어 알고리즘 구현하기, Control Block States and Output of Enabled Subsystem, Merging Signals 항목을 참조하십시오.

예제

Enabled Subsystem을 사용하여 제어 알고리즘 구현하기

이 예제에서는 Enabled Subsystem을 사용하여 이진 논리형 신호를 기반으로 제어 알고리즘을 구현하는 방법을 보여줍니다. Enabled Subsystem은 이진 신호가 양수 값을 갖고 제어 알고리즘을 구현할 때 실행됩니다. 이 예제에서는 불안정한 동적 시스템을 안정화하는 데 슈퍼 트위스팅(super-twisting) 제어 알고리즘이 사용됩니다. 슈퍼 트위스팅(super-twisting) 알고리즘은 강력한 성능으로 잘 알려진 슬라이딩 모드 제어 기법 중 하나입니다.

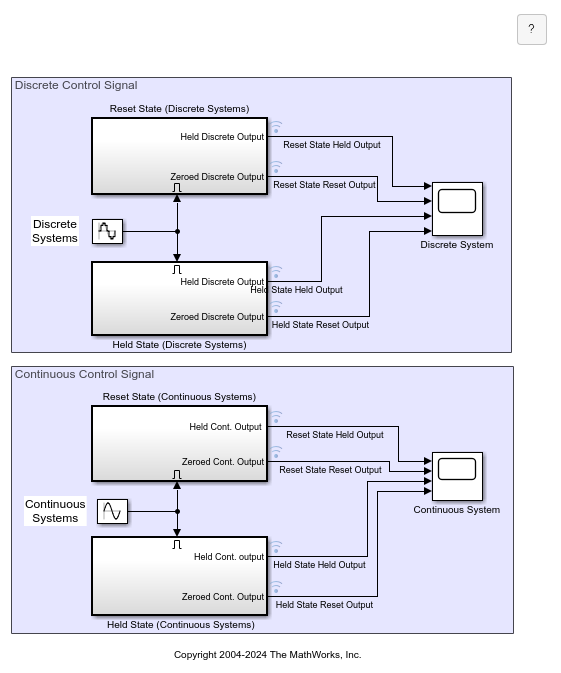

Control Block States and Output of Enabled Subsystem

Reset or hold states of blocks inside an Enabled Subsystem block when the subsystem is disabled and how to control the subsystem output. In this example, you see four different combinations of state and output value configurations for both discrete and continuous control signals. When the enabled subsystem is disabled, the combinations work as follows:

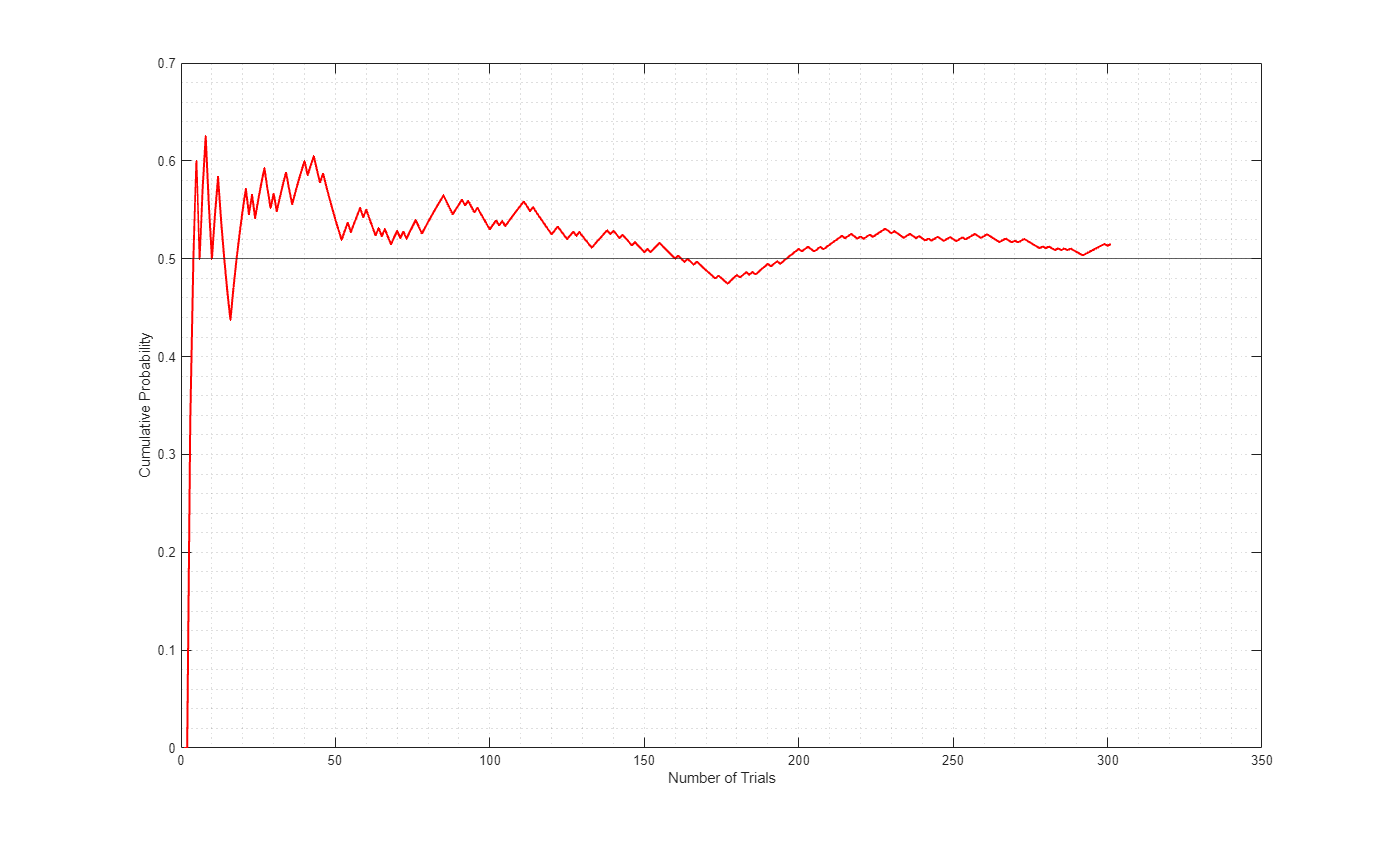

Exploring Law of Large Numbers using MATLAB System Block

Use MATLAB System blocks to illustrate the law of large numbers in Simulink.

Counters Using Conditionally Executed Subsystems

Implement counters using Enabled and Triggered subsystems. In this example, the model sldemo_counters controls flow of water into a tank and uses a counter to count the number of times overflow occurs, where overflow occurs when the water level in the tank is 8 meters or more for 30 seconds or more.

Building a Clutch Lock-Up Model

Use Simulink® to model and simulate a rotating clutch system. Although modeling a clutch system is difficult because of topological changes in the system dynamics during lockup, this example shows how enabled subsystem can easily handle such problems. We illustrate how to employ important Simulink modeling concepts in the creation of the clutch simulation. Designers can apply these concepts to many models with strong discontinuities and constraints that may change dynamically.

포트

입력

Subsystem 블록에 대한 신호 입력으로, 스칼라, 벡터 또는 행렬로 지정됩니다. 서브시스템 내에 Inport 블록을 배치하면 Subsystem 블록에 외부 입력 포트가 추가됩니다. 포트 레이블은 Inport 블록의 이름과 일치합니다.

Inport 블록을 사용하여 로컬 환경에서 신호를 받습니다.

데이터형: half | single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point | enumerated | bus | image

서브시스템 내의 Enable 블록은 Subsystem 블록에 외부 입력 포트를 추가하고 블록을 Enabled Subsystem 블록으로 만듭니다.

데이터형: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point

출력

Subsystem 블록의 신호 출력으로, 스칼라, 벡터 또는 행렬로 반환됩니다. 서브시스템 내에 Outport 블록을 배치하면 Subsystem 블록에 외부 출력 포트가 추가됩니다. 포트 레이블은 Outport 블록의 이름과 일치합니다.

Outport 블록을 사용하여 로컬 환경으로 신호를 보냅니다.

데이터형: half | single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point | enumerated | bus | image

파라미터

블록 파라미터를 대화형 방식으로 편집하려면 속성 인스펙터를 사용합니다. Simulink® 툴스트립의 시뮬레이션 탭에 있는 준비 갤러리에서 속성 인스펙터를 선택하십시오.

기본

Subsystem 블록 아이콘에 포트 레이블을 표시하는 방법을 선택합니다.

안 함— 포트 레이블을 표시하지 않습니다.FromPortIcon— 해당 포트 아이콘에 신호 이름이 표시되면 Subsystem 블록에 신호 이름을 표시합니다. 그렇지 않은 경우 포트 블록 이름을 표시하거나, 블록 이름이 디폴트 이름이면 포트 번호를 표시합니다.FromPortBlockName— Subsystem 블록에 해당 포트 블록의 이름을 표시합니다.SignalName— 포트에 연결된 신호가 명명된 경우 Subsystem 블록에 신호의 이름을 표시합니다. 그렇지 않은 경우 해당 포트 블록의 이름을 표시합니다.

Subsystem 블록의 포트 레이블 편집에 대한 자세한 내용은 Edit Port Labels on Subsystem Blocks 항목을 참조하십시오.

프로그래밍 방식의 사용법

프로그래밍 방식으로 블록 파라미터 값을 설정하려면 set_param 함수를 사용하십시오.

| 파라미터: | ShowPortLabels |

| 값: | 'FromPortIcon' (디폴트 값) | 'FromPortBlockName' | 'SignalName' | 'none' |

서브시스템의 내용에 대한 사용자 액세스를 제어합니다.

ReadWrite— 서브시스템 내용을 열고 수정할 수 있습니다.ReadOnly— 서브시스템을 열 수 있지만 수정할 수는 없습니다. 서브시스템이 블록 라이브러리에 있는 경우 서브시스템에 대한 링크를 만들고 열 수 있으며 서브시스템의 로컬 복사본을 만들고 수정할 수 있습니다. 하지만 원래 라이브러리 인스턴스의 내용을 수정하거나 권한을 변경할 수는 없습니다.NoReadOrWrite— 서브시스템을 열거나 수정할 수 없습니다. 서브시스템이 라이브러리에 있는 경우 모델의 서브시스템에 대한 링크를 만들 수 있지만 열거나 수정하거나 권한을 변경하거나 서브시스템의 로컬 복사본을 만들 수는 없습니다.

읽기/쓰기 권한 파라미터가 NoReadOrWrite로 설정된 서브시스템의 내용을 보려고 시도해도 반응이 없습니다. 예를 들어, 이러한 서브시스템을 더블 클릭해도 해당 서브시스템이 열리지 않으며 어떤 메시지도 표시되지 않습니다.

프로그래밍 방식의 사용법

프로그래밍 방식으로 블록 파라미터 값을 설정하려면 set_param 함수를 사용하십시오.

| 파라미터: | Permissions |

| 값: | 'ReadWrite' (디폴트 값) | 'ReadOnly' | 'NoReadOrWrite' |

서브시스템이 실행되는 동안 오류가 발생할 경우 호출할 함수의 이름을 입력합니다.

서브시스템의 핸들과 오류 유형을 지정하는 문자형 벡터, 이렇게 두 인수가 함수에 전달됩니다. 지정된 함수가 없는 경우 서브시스템 실행 시 오류가 발생하면 일반 오류 메시지가 표시됩니다.

프로그래밍 방식의 사용법

프로그래밍 방식으로 블록 파라미터 값을 설정하려면 set_param 함수를 사용하십시오.

| 파라미터: | ErrorFcn |

| 값: | '' (디폴트 값) | function name in quotes |

| 데이터형: | char | string |

이 서브시스템에서 참조하는 작업 공간 변수의 이름과 연결을 맺어야 할지 여부를 선택합니다.

자세한 내용은 Symbol Resolution 및 Symbol Resolution Process 항목을 참조하십시오.

모두— 블록 파라미터 값과 Simulink 데이터 객체를 지정하는 데 사용되는 변수를 포함하여 이 서브시스템에서 사용되는 모든 작업 공간 변수의 이름과 연결을 맺습니다(예:Simulink.Signal객체).ExplicitOnly— 블록 파라미터 값, 데이터 저장소 메모리(블록이 없는 경우), 신호, 그리고 “연결이 맺어져야 함”으로 표시된 상태를 지정하는 데 사용되는 작업 공간 변수의 이름과만 연결을 맺습니다.안 함— 어떠한 작업 공간 변수 이름과도 연결을 맺지 않습니다.

프로그래밍 방식의 사용법

프로그래밍 방식으로 블록 파라미터 값을 설정하려면 set_param 함수를 사용하십시오.

| 파라미터: | PermitHierarchicalResolution |

| 값: | 'All' (디폴트 값) | 'ExplicitOnly' | 'None' |

재초기화 이벤트 포트를 표시하려면 이 파라미터를 선택하십시오. 포트를 제거하려면 이 파라미터를 선택 해제하십시오.

종속성

이 파라미터를 활성화하려면 아토믹 단위로 처리를 선택하십시오.

프로그래밍 방식의 사용법

프로그래밍 방식으로 블록 파라미터 값을 설정하려면 set_param 함수를 사용하십시오.

| 파라미터: | ShowSubsystemReinitializePorts |

| 값: | 'off' (디폴트 값) | 'on' |

Atomic Subsystem을 포함하는 인위적 대수 루프의 제거를 시도합니다.

off— Atomic Subsystem을 포함하는 인위적 대수 루프를 제거하려고 시도하지 않습니다.on— Atomic Subsystem을 포함하는 인위적 대수 루프를 제거하려고 시도합니다.

종속성

이 파라미터를 활성화하려면 아토믹 단위로 처리를 선택하십시오.

프로그래밍 방식의 사용법

프로그래밍 방식으로 블록 파라미터 값을 설정하려면 set_param 함수를 사용하십시오.

| 파라미터: | MinAlgLoopOccurrences |

| 값: | 'off' (디폴트 값) | 'on' |

코드 생성

코드 생성 탭의 파라미터를 사용하려면 Simulink Coder™ 라이선스 또는 Embedded Coder® 라이선스가 필요합니다.

아토믹(비가상) 서브시스템에 대해 생성할 코드 형식을 선택합니다.

자동— 모델에 존재하는 서브시스템 인스턴스의 유형과 수를 기반으로 최적의 형식이 선택됩니다.인라인— 서브시스템이 무조건 인라인으로 처리됩니다.재사용 불가 함수— 파일 이름 옵션이자동으로 설정된 경우 모델 파일 내에 개별 함수들이 패키징됩니다. 파일 이름 옵션이서브시스템 이름 사용,함수 이름 사용또는사용자 지정으로 설정되어 각기 다른 파일 이름이 사용되는 경우 개별 함수들이 각각의 개별 파일로 패키징됩니다.이 설정을 사용하는 서브시스템은 함수 인터페이스 파라미터 설정에 따라 인수를 가질 수 있는 함수를 생성합니다. 함수 이름 파라미터 및 파일 이름(확장자 없음) 파라미터를 각각 사용하여, 생성되는 함수와 파일의 이름을 지정할 수 있습니다. 이러한 함수는 재진입 함수가 아닙니다.

재사용 가능 함수— 모델에 서브시스템의 인스턴스가 여러 개 포함된 경우 서브시스템 코드 재사용을 허용하는 인수가 있는 함수가 생성됩니다.또한 이 옵션을 선택할 경우, 생성되는 함수는 참조된 모델 전체에 서브시스템의 인스턴스가 여럿 포함된 모델 참조 계층 구조의 생성된 코드에서 서브시스템 코드를 재사용하는 것을 허용하는 인수를 갖게 됩니다. 이 경우 서브시스템은 라이브러리에 있어야 합니다.

자세한 내용은 다음 항목을 참조하십시오.

Generate Inlined Subsystem Code (Simulink Coder)

Generate Subsystem Code as Separate Function and Files (Simulink Coder)

Generate Reusable Code from Library Subsystems Shared Across Models (Simulink Coder)

디폴트 값은 블록 구성에 따라 달라집니다. 예를 들어, Subsystem 블록의 디폴트 값은 자동입니다. CodeReuseSubsystem 블록의 디폴트 값은 재사용 가능 함수입니다.

팁

서브시스템의 여러 인스턴스를 하나의 재사용 가능 함수로 표현하려는 경우 각각을

자동또는재사용 가능 함수로 지정할 수 있습니다. 두 옵션을 모두 사용하면 지정할 때마다 하나씩 두 개의 재사용 가능 함수가 생성되므로 둘 중 하나만 사용하는 것이 좋습니다. 이러한 옵션의 결과는 재사용이 불가능할 때만 다릅니다.자동을 선택하면 서브시스템 코드의 함수나 파일 이름을 제어할 수 없습니다.재사용 가능 함수옵션과자동옵션은 둘 다 서브시스템의 여러 인스턴스가 존재하는지 여부와 코드 재사용 가능 여부를 확인하려고 합니다. 각 옵션 동작의 차이점은 재사용이 불가능할 때 다음과 같이 나타납니다.자동을 선택하면 인라인 코드가 생성되며, 인라인이 금지되는 상황이라면 각 서브시스템 인스턴스에 대해 별개의 함수가 생성됩니다.재사용 가능 함수를 선택하면 모델의 각 서브시스템 인스턴스에 대해 인수를 포함한 별개의 함수가 생성됩니다.

생성된 코드가 소스 컨트롤 상태에 있는 동안

재사용 가능 함수를 선택하는 경우 파일 이름 옵션을서브시스템 이름 사용,함수 이름 사용또는사용자 지정으로 설정하십시오. 그러지 않으면 모델을 수정할 때마다 코드 파일의 이름이 변경되어 파일에 소스 컨트롤을 적용할 수 없게 됩니다.자동또는인라인이외의 옵션과 함께 모델 구성 파라미터 상태를 선택하면 코드 생성기는 별개의 출력 메서드와 업데이트 메서드를 생성합니다. 코드 생성기는 코드 생성 및 시뮬레이션을 위한 출력 메서드와 업데이트 메서드의 결합 사양을 고려하지 않습니다.

종속성

이 파라미터는 코드 생성 시 Simulink Coder 라이선스가 필요합니다.

이 파라미터를 활성화하려면 아토믹 단위로 처리를 선택하십시오.

프로그래밍 방식의 사용법

프로그래밍 방식으로 블록 파라미터 값을 설정하려면 set_param 함수를 사용하십시오.

| 파라미터: | RTWSystemCode |

| 값: | 'Auto' | 'Inline' | 'Nonreusable function' | 'Reusable function' |

소프트웨어가 서브시스템에 대해 생성하는 함수를 명명하는 방법을 선택합니다.

Embedded Coder 라이선스가 있는 경우 구성 파라미터 코드 생성 > 식별자 창의 옵션을 사용하여 함수 이름을 제어할 수 있습니다.

자동— 디폴트 명명 규칙인model_subsystem()model은 모델 이름이고subsystem은 서브시스템의 이름이거나, 코드가 재사용되는 경우 동일한 서브시스템의 이름입니다.함수 패키징 파라미터에

재사용 가능 함수를 선택하고 모델 참조 계층 구조에 재사용 가능한 서브시스템의 인스턴스가 여럿 포함되어 있는 경우 서브시스템에 재사용 가능한 코드를 생성하려면 함수 이름 옵션을자동으로 설정해야 합니다.서브시스템 이름 사용— 서브시스템 이름을 함수 이름으로 사용합니다. 기본적으로, 함수 이름은 명명 규칙model_subsystem서브시스템이 라이브러리 블록에 있고 서브시스템 파라미터 함수 패키징이

재사용 가능 함수로 설정되어 있는 경우서브시스템 이름 사용옵션을 설정하면 코드 생성기는 서브시스템 함수 이름과 파일 이름으로 라이브러리 블록 이름을 사용합니다.사용자 지정— 함수 이름 필드를 활성화합니다. 유효한 C 또는 C++ 함수 이름을 입력합니다. 이때 함수 이름은 고유해야 합니다.

자세한 내용은 Generate Subsystem Code as Separate Function and Files (Simulink Coder) 항목을 참조하십시오.

디폴트 값은 블록 구성에 따라 달라집니다. 예를 들어, Subsystem 블록의 디폴트 값은 자동입니다. CodeReuseSubsystem 블록의 디폴트 값은 서브시스템 이름 사용입니다.

종속성

이 파라미터에는 Simulink Coder 라이선스가 필요합니다.

이 파라미터를 활성화하려면 함수 패키징을

재사용 불가 함수또는재사용 가능 함수로 설정하십시오.

프로그래밍 방식의 사용법

프로그래밍 방식으로 블록 파라미터 값을 설정하려면 set_param 함수를 사용하십시오.

| 파라미터: | RTWFcnNameOpts |

| 값: | 'Auto' | 'Use subsystem name' | 'User specified' |

서브시스템 코드에 대해 고유하고 유효한 C 또는 C++ 함수 이름을 지정합니다.

Simulink Coder 코드 생성기가 자동 생성된 자체 이름을 할당하거나 서브시스템 이름을 사용하게 두지 않고 함수에 특정 이름을 지정하려면 이 파라미터를 사용하십시오. 자세한 내용은 Generate Subsystem Code as Separate Function and Files (Simulink Coder) 항목을 참조하십시오.

종속성

이 파라미터에는 Simulink Coder 라이선스가 필요합니다.

이 파라미터를 활성화하려면 함수 이름 옵션을

사용자 지정으로 설정하십시오.

프로그래밍 방식의 사용법

프로그래밍 방식으로 블록 파라미터 값을 설정하려면 set_param 함수를 사용하십시오.

| 파라미터: | RTWFcnName |

| 값: | '' (디폴트 값) | function name in quotes |

| 데이터형: | char | string |

서브시스템에 대한 함수를 생성할 때 적용되는, 함수의 개별 파일에 대한 명명 방법을 선택합니다.

자동— 서브시스템 구성과 모델에 있는 인스턴스 수에 따라자동을 선택한 결과가 달라집니다.코드 생성기가 서브시스템에 대한 별개의 파일을 생성하지 않는 경우 서브시스템 코드는 서브시스템의 부모 시스템에서 생성된 코드 모듈 내에 생성됩니다. 서브시스템 부모가 모델 자체인 경우

model.cmodel.cpp함수 패키징 파라미터에

재사용 가능 함수를 선택하고 생성된 코드가 소스 컨트롤 상태에 있는 경우 파일 이름 옵션에자동이외의 값을 지정해 보십시오. 이렇게 하면 생성된 파일 이름이 관련 없는 모델 수정으로 인해 변경되어 소스 컨트롤을 사용하여 구성을 관리할 때 문제가 되는 상황을 방지할 수 있습니다.함수 패키징 파라미터에

재사용 가능 함수를 선택하고 모델 참조 계층 구조에 재사용 가능한 서브시스템의 인스턴스가 여럿 포함되어 있는 경우 서브시스템에 재사용 가능한 코드를 생성하려면 파일 이름 옵션을자동으로 설정해야 합니다.

서브시스템 이름 사용— 코드 생성기는 서브시스템(또는 라이브러리 블록) 이름을 파일 이름으로 사용하여 별개의 파일을 생성합니다.파일 이름 옵션이

서브시스템 이름 사용으로 설정되어 있으면, 모델에 Model 블록이 포함되어 있거나 모델에 대한 모델 참조 타깃이 생성되는 경우 서브시스템 파일 이름이 변형됩니다. 이런 경우 서브시스템의 파일 이름은 서브시스템 이름 앞에 모델 이름이 오는 형태로 구성됩니다.함수 이름 사용— 코드 생성기는 함수 이름 옵션에서 지정한 함수 이름을 파일 이름으로 사용합니다.사용자 지정— 이 옵션을 선택하면 파일 이름(확장자 없음) 텍스트 입력 필드가 활성화됩니다. 코드 생성기는 사용자가 입력하는 이름을 파일 이름으로 사용합니다. 파일 이름을 입력하되,.c또는.cpp확장자(또는 기타 확장자)를 포함하지 마십시오. 이 파일 이름은 고유하지 않아도 됩니다.서브시스템 소스 파일 이름은 고유하지 않아도 되지만, 순환 종속 관계를 초래하는 고유하지 않은 이름을 입력하면 안 됩니다. 예를 들어,

sys_a.h에는sys_b.h가 포함되고,sys_b.h에는sys_c.h가 포함되며,sys_c.h에는sys_a.h가 포함되는 경우가 이에 해당합니다.

디폴트 값은 블록 구성에 따라 달라집니다. 예를 들어, Subsystem 블록의 디폴트 값은 자동입니다. CodeReuseSubsystem 블록의 디폴트 값은 함수 이름 사용입니다.

종속성

이 파라미터에는 Simulink Coder 라이선스가 필요합니다.

이 파라미터를 활성화하려면 함수 패키징을

재사용 불가 함수또는재사용 가능 함수로 설정하십시오.

프로그래밍 방식의 사용법

프로그래밍 방식으로 블록 파라미터 값을 설정하려면 set_param 함수를 사용하십시오.

| 파라미터: | RTWFileNameOpts |

| 값: | 'Auto' | 'Use subsystem name' | 'Use function name' | 'User specified' |

고유한 파일 이름을 지정할 필요가 없습니다. 하지만 순환 종속 관계를 초래하는 고유하지 않은 이름을 입력하지는 마십시오. 예를 들어, sys_a.h에는 sys_b.h가 포함되고, sys_b.h에는 sys_c.h가 포함되며, sys_c.h에는 sys_a.h가 포함되는 경우가 이에 해당합니다.

자세한 내용은 Generate Subsystem Code as Separate Function and Files (Simulink Coder) 항목을 참조하십시오.

종속성

이 파라미터에는 Simulink Coder 라이선스가 필요합니다.

이 파라미터를 활성화하려면 파일 이름 옵션을

사용자 지정으로 설정하십시오.

프로그래밍 방식의 사용법

프로그래밍 방식으로 블록 파라미터 값을 설정하려면 set_param 함수를 사용하십시오.

| 파라미터: | RTWFileName |

| 값: | '' (디폴트 값) | filename in quotes |

| 데이터형: | char | string |

생성된 함수에 인수를 사용하는 방법을 선택합니다.

void_void— 인수 없이 함수를 생성하고 데이터를 전역 변수로 전달합니다. 예를 들면 다음과 같습니다.void subsystem_function(void)

인수 허용(최적화됨)— 데이터를 전역 변수로 전달하는 대신 인수를 사용하는 함수를 생성합니다. 이 옵션을 지정하면 전역 RAM이 줄어듭니다. 이 옵션을 사용하면 코드 크기가 감소하고 실행 속도가 향상되며 코드 생성기가 최적화를 추가로 적용하도록 할 수 있습니다. 예를 들면 다음과 같습니다.void subsystem_function(real_T rtu_In1, real_T rtu_In2, real_T *rty_Out1)일부 경우에는 최적화된 코드를 생성할 때 코드 생성기가 인수를 갖는 함수를 생성하지 않을 수도 있습니다.

인수 허용(그래픽 인터페이스와 일치)— Subsystem 그래픽 블록 인터페이스와 일치하는 인수를 사용하는 함수 인터페이스를 생성합니다. 생성된 함수 인터페이스는 예측 가능하며 변경되지 않습니다. 예측 가능한 인터페이스는 코드를 디버깅 및 테스트하고 외부 애플리케이션과 통합하는 데 유용할 수 있습니다. 예를 들어 모델에 Inport 블록 2개와 Outport 블록 2개가 있는 경우 생성되는 함수 인터페이스는 다음과 같습니다.void subsystem_function(real_T rtu_In1, real_T rtu_In2, real_T *rty_Out1, real_T *rty_Out2)

자세한 내용은 다음 항목을 참조하십시오.

Reduce Global Variables in Nonreusable Subsystem Functions (Embedded Coder)

Generate Predictable Function Interface to Match Graphical Block Interface (Embedded Coder)

Generate Modular Function Code for Nonvirtual Subsystems (Embedded Coder)

종속성

이 파라미터에는 Embedded Coder 라이선스와 ERT 기반 시스템 타깃 파일이 필요합니다.

이 파라미터를 활성화하려면 함수 패키징을

재사용 불가 함수로 설정하십시오.

프로그래밍 방식의 사용법

프로그래밍 방식으로 블록 파라미터 값을 설정하려면 set_param 함수를 사용하십시오.

| 파라미터: | FunctionInterfaceSpec |

| 값: | 'void_void' (디폴트 값) | 'Allow arguments (Optimized)' | 'Allow arguments (Match graphical interface)' |

Atomic Subsystem에 대한 내부 데이터가 부모 모델로부터 분리되 서브시스템의 소유가 되는 서브시스템 함수 코드를 생성합니다.

off— Atomic Subsystem에 대한 내부 데이터가 부모 모델로부터 분리되어 서브시스템의 소유가 되는 서브시스템 함수 코드를 생성하지 않습니다.on— Atomic Subsystem에 대한 내부 데이터가 부모 모델로부터 분리되어 서브시스템의 소유가 되는 서브시스템 함수 코드를 생성합니다. 서브시스템 데이터 구조체는 부모 모델 데이터 구조체와는 별개로 선언됩니다. 별도의 데이터를 갖는 서브시스템은 자체의 블록 I/O 및DWork데이터 구조체를 가집니다. 결과적으로, 서브시스템에 대해 생성된 코드를 더 쉽게 추적하고 테스트할 수 있습니다. 또한 데이터 분리에 의해 여러 데이터 구조체로 분할되기 때문에 보통은 모델 전체에서 전역 데이터 구조체의 최대 크기가 줄어들게 됩니다.

Atomic Subsystem의 모듈식 함수 코드를 생성하는 방법에 대한 자세한 내용은 Generate Modular Function Code for Nonvirtual Subsystems (Embedded Coder) 항목을 참조하십시오.

Atomic Subsystem에 메모리 섹션을 적용하는 방법에 대한 자세한 내용은 Override Default Memory Placement for Subsystem Functions and Data (Embedded Coder) 항목을 참조하십시오.

종속성

이 파라미터에는 Embedded Coder 라이선스와 ERT 기반 시스템 타깃 파일이 필요합니다.

이 파라미터를 활성화하려면 함수 패키징을

재사용 불가 함수로 설정하십시오.

프로그래밍 방식의 사용법

프로그래밍 방식으로 블록 파라미터 값을 설정하려면 set_param 함수를 사용하십시오.

| 파라미터: | FunctionWithSeparateData |

| 값: | 'off' (디폴트 값) | 'on' |

서브시스템 초기화 함수 및 종료 함수에 메모리 섹션을 적용하는 방법을 선택합니다.

모델에서 상속— 서브시스템 함수 코드에 루트 모델 메모리 섹션을 적용합니다.디폴트 값— 서브시스템 시스템 코드에 메모리 섹션을 적용하지 않으며 모델 수준 사양은 무시됩니다.모델 메모리 섹션 중 하나를 서브시스템에 적용합니다.

팁

가능한 값은 모델 구성에 대해 설정한 메모리 섹션 패키지(있는 경우)에 따라 달라집니다. Control Data and Function Placement in Memory by Inserting Pragmas (Embedded Coder) 및 Model Configuration Parameters: Code Generation (Simulink Coder) 항목을 참조하십시오.

패키지로 모델을 구성하지 않은 경우에는

모델에서 상속값만 사용할 수 있습니다. 그 외의 경우에는 목록에디폴트 값과 모델 패키지에 있는 모든 메모리 섹션이 포함됩니다.이러한 옵션은 지정된 서브시스템의 모델 메모리 섹션 설정을 재정의하는 데 유용할 수 있습니다. Atomic Subsystem에 메모리 섹션을 적용하는 방법에 대한 자세한 내용은 Override Default Memory Placement for Subsystem Functions and Data (Embedded Coder) 항목을 참조하십시오.

종속성

이 파라미터에는 Embedded Coder 라이선스와 ERT 기반 시스템 타깃 파일이 필요합니다.

이 파라미터를 활성화하려면 함수 패키징을

재사용 불가 함수또는재사용 가능 함수로 설정하십시오.

프로그래밍 방식의 사용법

프로그래밍 방식으로 블록 파라미터 값을 설정하려면 set_param 함수를 사용하십시오.

| 파라미터: | RTWMemSecFuncInitTerm |

| 값: | 'Inherit from model' (디폴트 값) | 'Default' | model memory section in quotes |

Embedded Coder가 서브시스템 실행 함수에 메모리 섹션을 적용하는 방법을 선택합니다.

모델에서 상속— 서브시스템 함수 코드에 루트 모델 메모리 섹션을 적용합니다.디폴트 값— 서브시스템 시스템 코드에 메모리 섹션을 적용하지 않으며 모델 수준 사양은 무시됩니다.모델 메모리 섹션 중 하나를 서브시스템에 적용합니다.

팁

가능한 값은 모델 구성에 대해 설정한 메모리 섹션 패키지(있는 경우)에 따라 달라집니다. Control Data and Function Placement in Memory by Inserting Pragmas (Embedded Coder) 및 Model Configuration Parameters: Code Generation (Simulink Coder) 항목을 참조하십시오.

패키지로 모델을 구성하지 않은 경우에는

모델에서 상속값만 사용할 수 있습니다. 그 외의 경우에는 목록에디폴트 값과 모델 패키지에 있는 모든 메모리 섹션이 포함됩니다.이러한 옵션은 지정된 서브시스템의 모델 메모리 섹션 설정을 재정의하는 데 유용할 수 있습니다. Atomic Subsystem에 메모리 섹션을 적용하는 방법에 대한 자세한 내용은 Override Default Memory Placement for Subsystem Functions and Data (Embedded Coder) 항목을 참조하십시오.

종속성

이 파라미터에는 Embedded Coder 라이선스와 ERT 기반 시스템 타깃 파일이 필요합니다.

이 파라미터를 활성화하려면 함수 패키징을

재사용 불가 함수또는재사용 가능 함수로 설정하십시오.

프로그래밍 방식의 사용법

프로그래밍 방식으로 블록 파라미터 값을 설정하려면 set_param 함수를 사용하십시오.

| 파라미터: | RTWMemSecFuncExecute |

| 값: | 'Inherit from model' (디폴트 값) | 'Default' | model memory section in quotes |

소프트웨어가 서브시스템 상수에 메모리 섹션을 적용하는 방법을 선택합니다.

모델에서 상속— 서브시스템 데이터에 루트 모델 메모리 섹션을 적용합니다.디폴트 값— 서브시스템 데이터에 메모리 섹션을 적용하지 않으며 모델 수준 사양은 무시됩니다.모델 메모리 섹션 중 하나를 서브시스템에 적용합니다.

팁

여기서 지정하는 메모리 섹션이 생성된 코드의 해당 전역 데이터 구조체에 적용됩니다. Atomic Subsystem에 대해 생성된 전역 데이터 구조체에 대한 기본 정보는 Standard Data Structures (Simulink Coder) 항목을 참조하십시오.

가능한 값은 모델 구성에 대해 설정한 메모리 섹션 패키지(있는 경우)에 따라 달라집니다. Control Data and Function Placement in Memory by Inserting Pragmas (Embedded Coder) 항목을 참조하십시오.

패키지로 모델을 구성하지 않은 경우에는

모델에서 상속값만 사용할 수 있습니다. 그 외의 경우에는 목록에디폴트 값과 모델 패키지에 있는 모든 메모리 섹션이 포함됩니다.이러한 옵션은 지정된 서브시스템의 모델 메모리 섹션 설정을 재정의하는 데 유용할 수 있습니다. Atomic Subsystem에 메모리 섹션을 적용하는 방법에 대한 자세한 내용은 Override Default Memory Placement for Subsystem Functions and Data (Embedded Coder) 항목을 참조하십시오.

종속성

이 파라미터에는 Embedded Coder 라이선스와 ERT 기반 시스템 타깃 파일이 필요합니다.

이 파라미터를 활성화하려면 함수 패키징을

재사용 불가 함수로 설정하고 별도의 데이터를 갖는 함수 파라미터를 선택하십시오.

프로그래밍 방식의 사용법

프로그래밍 방식으로 블록 파라미터 값을 설정하려면 set_param 함수를 사용하십시오.

| 파라미터: | RTWMemSecDataConstants |

| 값: | 'Inherit from model' (디폴트 값) | 'Default' | model memory section in quotes |

서브시스템 내부 데이터에 메모리 섹션을 적용하는 방법을 선택합니다.

모델에서 상속— 서브시스템 데이터에 루트 모델 메모리 섹션을 적용합니다.디폴트 값— 서브시스템 데이터에 메모리 섹션을 적용하지 않으며 모델 수준 사양은 무시됩니다.모델 메모리 섹션 중 하나를 서브시스템에 적용합니다.

팁

여기서 지정하는 메모리 섹션이 생성된 코드의 해당 전역 데이터 구조체에 적용됩니다. Atomic Subsystem에 대해 생성된 전역 데이터 구조체에 대한 기본 정보는 Standard Data Structures (Simulink Coder) 항목을 참조하십시오.

가능한 값은 모델 구성에 대해 설정한 메모리 섹션 패키지(있는 경우)에 따라 달라집니다. Control Data and Function Placement in Memory by Inserting Pragmas (Embedded Coder) 항목을 참조하십시오.

패키지로 모델을 구성하지 않은 경우에는

모델에서 상속값만 사용할 수 있습니다. 그 외의 경우에는 목록에디폴트 값과 모델 패키지에 있는 모든 메모리 섹션이 포함됩니다.이러한 옵션은 지정된 서브시스템의 모델 메모리 섹션 설정을 재정의하는 데 유용할 수 있습니다. Atomic Subsystem에 메모리 섹션을 적용하는 방법에 대한 자세한 내용은 Override Default Memory Placement for Subsystem Functions and Data (Embedded Coder) 항목을 참조하십시오.

종속성

이 파라미터에는 Embedded Coder 라이선스와 ERT 기반 시스템 타깃 파일이 필요합니다.

이 파라미터를 활성화하려면 함수 패키징을

재사용 불가 함수로 설정하고 별도의 데이터를 갖는 함수 파라미터를 선택하십시오.

프로그래밍 방식의 사용법

프로그래밍 방식으로 블록 파라미터 값을 설정하려면 set_param 함수를 사용하십시오.

| 파라미터: | RTWMemSecDataInternal |

| 값: | 'Inherit from model' (디폴트 값) | 'Default' | model memory section in quotes |

서브시스템 파라미터에 메모리 섹션을 적용하는 방법을 선택합니다.

모델에서 상속— 서브시스템 함수 코드에 루트 모델 메모리 섹션을 적용합니다.디폴트 값— 서브시스템 시스템 코드에 메모리 섹션을 적용하지 않으며 모델 수준 사양은 무시됩니다.모델 메모리 섹션 중 하나를 서브시스템에 적용합니다.

팁

여기서 지정하는 메모리 섹션이 생성된 코드의 해당 전역 데이터 구조체에 적용됩니다. Atomic Subsystem에 대해 생성된 전역 데이터 구조체에 대한 기본 정보는 Standard Data Structures (Simulink Coder) 항목을 참조하십시오.

가능한 값은 모델 구성에 대해 설정한 메모리 섹션 패키지(있는 경우)에 따라 달라집니다. Control Data and Function Placement in Memory by Inserting Pragmas (Embedded Coder) 항목을 참조하십시오.

패키지로 모델을 구성하지 않은 경우에는

모델에서 상속값만 사용할 수 있습니다. 그 외의 경우에는 목록에디폴트 값과 모델 패키지에 있는 모든 메모리 섹션이 포함됩니다.이러한 옵션은 지정된 서브시스템의 모델 메모리 섹션 설정을 재정의하는 데 유용할 수 있습니다. Atomic Subsystem에 메모리 섹션을 적용하는 방법에 대한 자세한 내용은 Override Default Memory Placement for Subsystem Functions and Data (Embedded Coder) 항목을 참조하십시오.

종속성

이 파라미터에는 Embedded Coder 라이선스와 ERT 기반 시스템 타깃 파일이 필요합니다.

이 파라미터를 활성화하려면 함수 패키징을

재사용 불가 함수로 설정하고 별도의 데이터를 갖는 함수 파라미터를 선택하십시오.

프로그래밍 방식의 사용법

프로그래밍 방식으로 블록 파라미터 값을 설정하려면 set_param 함수를 사용하십시오.

| 파라미터: | RTWMemSecDataParameters |

| 값: | 'Inherit from model' (디폴트 값) | 'Default' | model memory section in quotes |

서브시스템 참조

참조하려는 서브시스템 파일을 지정합니다. 서브시스템 참조에 대한 자세한 내용은 Create and Use Referenced Subsystems in Models 항목을 참조하십시오.

종속성

이 파라미터에 액세스하려면 서브시스템 참조 섹션에서 변환을 클릭하십시오.

서브시스템을 참조된 서브시스템으로 변환하는 방법에 대한 자세한 내용은 Convert Between Subsystems and Referenced Subsystems 항목을 참조하십시오.

프로그래밍 방식의 사용법

프로그래밍 방식으로 블록 파라미터 값을 설정하려면 set_param 함수를 사용하십시오.

| 파라미터: | ReferencedSubsystem |

| 값: | '' (디폴트 값) | subsystem filename in quotes |

| 데이터형: | char | string |

블록 특성

확장 기능

실제 코드 생성 지원은 블록 구현에 따라 달라집니다.

HDL Coder™는 HDL 구현과 합성된 논리에 영향을 주는 추가 구성 옵션을 제공합니다.

HDL 코드 생성을 목표로 한 모델에 Enabled Subsystem을 사용할 경우 다음 사항을 고려하는 것이 좋습니다.

합성 결과가 Simulink 결과와 일치하려면 인에이블 포트가 FPGA에 등록된 논리(동기식 클록)에 의해 구동되어야 합니다.

Enabled Subsystem 출력 신호에 단위 지연을 설정합니다. 그러면 코드 생성기가 HDL 코드에 바이패스 레지스터를 추가로 삽입하는 것이 방지됩니다.

Enabled Subsystem은 다음과 같이 합성 결과에 영향을 줄 수 있습니다.

경우에 따라 시스템 클록 속도가 조금 떨어질 수 있습니다.

생성된 코드는 더 많은 리소스를 사용하며, Enabled Subsystem 인스턴스 개수와 서브시스템별 출력 포트 개수로 스케일링됩니다.

| 아키텍처 | 설명 |

|---|---|

Module(디폴트 값) | 서브시스템 내에 서브시스템과 블록을 위한 코드를 생성합니다. |

BlackBox | 블랙박스 인터페이스를 생성합니다. 생성된 HDL 코드에는 서브시스템의 입력/출력 포트 정의만 포함됩니다. 그러므로 모델에서 서브시스템을 사용하여 수동으로 작성된 기존 HDL 코드에 인터페이스를 생성할 수 있습니다. 서브시스템에 블랙박스 인터페이스를 생성하는 것은 클록 신호 없이 Model 블록 인터페이스를 생성하는 것과 비슷합니다. |

| 생성된 코드에서 서브시스템을 제거합니다. 시뮬레이션에서 서브시스템을 사용할 수 있지만 HDL 코드에서 “no-op”로 간주합니다. |

| 일반 | |

|---|---|

| AdaptivePipelining | 합성 툴, 타깃 주파수, 곱셈기 워드 길이에 따른 자동 파이프라인 삽입입니다. 디폴트 값은 |

| BalanceDelays | 하나의 경로를 따라 새로운 지연이 발생하는 것을 감지하고 일치하는 지연을 다른 경로에 삽입합니다. 디폴트 값은 |

| ClockRatePipelining | 느린 데이터 레이트 대신 빠른 클록 속도로 파이프라인 레지스터를 삽입합니다. 디폴트 값은 |

| ConstrainedOutputPipeline | 기존 지연을 설계 내부로 이동하여 출력에 배치하는 레지스터 개수입니다. 분산된 파이프라이닝은 이러한 레지스터를 다시 분산하지 않습니다. 디폴트 값은 |

| DistributedPipelining | 파이프라인 레지스터 분산 또는 레지스터 타이밍 재지정입니다. 디폴트 값은 |

| DSPStyle | 곱셈기 매핑에 대한 합성 특성입니다. 디폴트 값은 |

| FlattenHierarchy | 생성된 HDL 코드에서 서브시스템 계층 구조를 제거합니다. 디폴트 값은 |

| InputPipeline | 생성된 코드에 삽입할 입력 파이프라인 단계의 개수입니다. 분산 파이프라이닝과 제약이 있는 출력 파이프라이닝은 이러한 레지스터를 이동할 수 있습니다. 디폴트 값은 |

| OutputPipeline | 생성된 코드에 삽입할 출력 파이프라인 단계의 개수입니다. 분산 파이프라이닝과 제약이 있는 출력 파이프라이닝은 이러한 레지스터를 이동할 수 있습니다. 디폴트 값은 |

| SharingFactor | 단일 공유 리소스에 매핑할 기능적으로 동일한 리소스 개수입니다. 디폴트 값은 0입니다. Resource Sharing (HDL Coder) 항목도 참조하십시오. |

| StreamingFactor | 직렬, 스칼라 데이터 경로로 변환하기 위해 시간 다중화된 병렬 데이터 경로 또는 벡터의 개수입니다. 디폴트 값은 0이며, 전체 병렬 데이터 경로를 구현합니다. Streaming (HDL Coder) 항목도 참조하십시오. |

타깃 지정

이 블록은 DUT가 될 수 없으므로 타깃 지정 탭의 블록 속성 설정은 무시됩니다.

HDL Coder는 다음 조건을 충족하는 Enabled Subsystem에 대해 HDL 코드 생성을 지원합니다.

Enabled Subsystem이 DUT가 아닙니다.

서브시스템이 트리거 상태와 활성화 상태 중 어느 쪽에도 해당하지 않습니다.

인에이블 신호가 스칼라입니다.

인에이블 신호의 입력 데이터형이 부울입니다.

서브시스템의 출력이 버스이면 아웃포트의 초기 조건은 0이어야 합니다.

인에이블 신호를 포함해 Enabled Subsystem의 모든 입력 및 출력이 동일한 레이트로 실행됩니다.

Enable 블록의 출력 포트 표시 파라미터가

끄기로 설정되어 있습니다.Enable 블록의 활성화할 때의 상태 파라미터가

유지로 설정되어 있습니다(즉, Enable 블록이 활성화될 때 상태를 재설정하지 않음).Enabled Subsystem 출력 포트의 비활성인 경우 출력 파라미터가

유지로 설정되어 있습니다(즉, Enabled Subsystem이 비활성될 때 출력을 재설정하지 않음).DUT에 다음 블록이 포함된 경우

RAMArchitecture가WithClockEnable로 설정되어 있습니다.Dual Port RAM

Simple Dual Port RAM

Single Port RAM

Enabled Subsystem에 다음 블록이 포함되어 있지 않습니다.

CIC Decimation

CIC Interpolation

FIR Decimation

FIR Interpolation

Downsample

Upsample

HDL FIFO

HDL Cosimulation 블록(HDL Verifier™)

Rate Transition

NR Polar Encoder 및 NR Polar Decoder(Wireless HDL Toolbox™)

hdlcoder_remove_redundant_logic 예제 모델은 HDL 코드 생성에서 Enabled Subsystem을 사용하는 방법을 보여줍니다. 이 예제를 열려면 다음을 입력하십시오.

openExample('hdlcoder/RemoveRedundantLogicGeneratedHDLCodeExample',... 'supportingFile','hdlcoder_remove_redundant_logic');

PLC 코드 생성

Simulink® PLC Coder™를 사용하여 Structured Text 코드를 생성할 수 있습니다.

실제 데이터형 지원은 블록 구현에 따라 다릅니다.

버전 내역

R2006a 이전에 개발됨

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

웹사이트 선택

번역된 콘텐츠를 보고 지역별 이벤트와 혜택을 살펴보려면 웹사이트를 선택하십시오. 현재 계신 지역에 따라 다음 웹사이트를 권장합니다:

또한 다음 목록에서 웹사이트를 선택하실 수도 있습니다.

사이트 성능 최적화 방법

최고의 사이트 성능을 위해 중국 사이트(중국어 또는 영어)를 선택하십시오. 현재 계신 지역에서는 다른 국가의 MathWorks 사이트 방문이 최적화되지 않았습니다.

미주

- América Latina (Español)

- Canada (English)

- United States (English)

유럽

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)