Software to AXI4-Stream

Libraries:

SoC Blockset /

Memory

Description

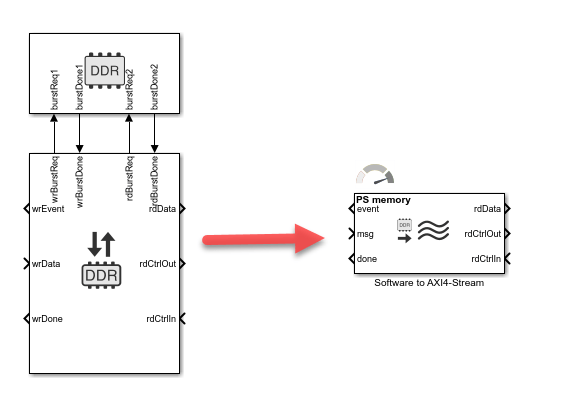

The Software to AXI4-Stream block models a connection between hardware logic and a software task through external memory. The writer (processor) streams data into the channel through a DMA driver using a MathWorks® simplified AXI stream protocol. The block models the datapath and software stack of that connection, including a FIFO, DMA engine, interconnect and external memory, interrupts, kernel buffer management of the DMA driver, and data transfers from the software task.

This block is equivalent to a Memory Channel block with the

Channel type parameter set to Software to AXI4-Stream via

DMA connected to a Memory Controller block.

Since the memory controller is implicit to the design - you can instantiate several memory blocks that connect to the same memory unit via a memory controller. Valid blocks are:

The maximum number of manager interfaces in a model is 16.

For more information about the MathWorks simplified AXI stream protocol, see AXI4-Stream Interface.

This image is a conceptual view of the block, streaming data from a processor algorithm to an FPGA algorithm.