이 번역 페이지는 최신 내용을 담고 있지 않습니다. 최신 내용을 영문으로 보려면 여기를 클릭하십시오.

If

if-else 구문과 유사한 논리를 사용하여 서브시스템 실행 선택

라이브러리:

Simulink /

Ports & Subsystems

설명

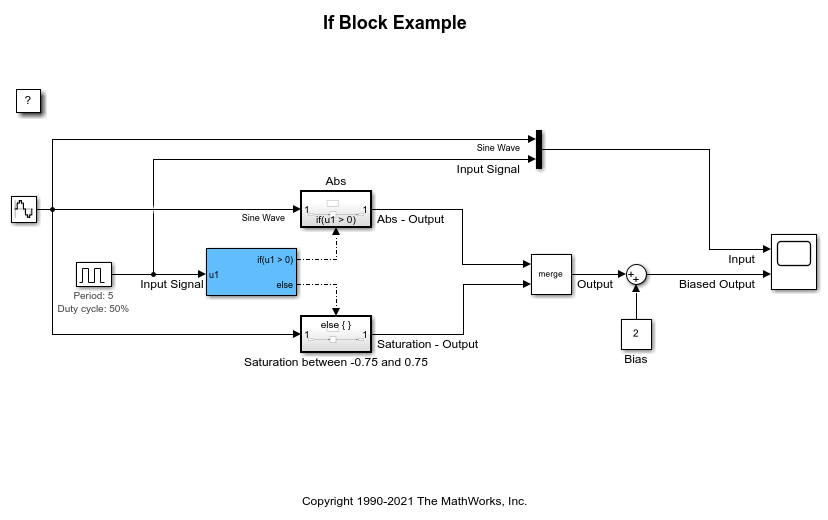

If 블록은 Action Port 블록을 포함하는 If Action Subsystem 블록과 함께 if-else 논리를 구현하여 서브시스템 실행을 제어합니다. If 블록을 사용하는 예제는 Select Subsystem Execution 항목을 참조하십시오.

예제

제한 사항

If 블록에는 다음과 같은 제한 사항이 있습니다.

조정 가능형 파라미터를 지원하지 않습니다.

if또는elseif표현식의 값은 표준 또는 액셀러레이터 모드에서 시뮬레이션 중이거나 생성된 코드를 실행하는 중에 조정될 수 없습니다.조정 가능형 if-else 표현식을 구현하려면 If 블록 외부에서 표현식을 조정하십시오. 예를 들어, Relational Operator 블록을 사용하여 If 블록 외부의 표현식을 평가하거나 조정 가능형 파라미터를 If 블록의 입력값으로 추가하면 됩니다.

사용자 지정 스토리지 클래스를 지원하지 않습니다. Organize Parameter Data into a Structure by Using Struct Storage Class (Embedded Coder) 항목을 참조하십시오.

if 표현식과 elseif 표현식에는

+,-,*,/와 같은 특정 연산자를 사용할 수 없습니다.

포트

입력

출력

파라미터

블록 특성

데이터형 |

|

직접 피드스루 |

|

다차원 신호 |

|

가변 크기 신호 |

|

영점교차 검출 |

|