Stateflow는 상태 천이도, 플로우 차트, 상태 천이표 및 진리표를 포함하는 그래픽 언어를 제공하는 제품입니다. Stateflow를 사용하면 입력 신호, 이벤트, 시간 기반 조건에 대한 MATLAB 알고리즘과 Simulink 모델의 반응을 설명할 수 있습니다.

Stateflow를 사용하면 감독 제어, 작업 스케줄링, 결함 관리, 통신 프로토콜, 사용자 인터페이스 및 하이브리드 시스템을 설계하고 개발할 수 있습니다.

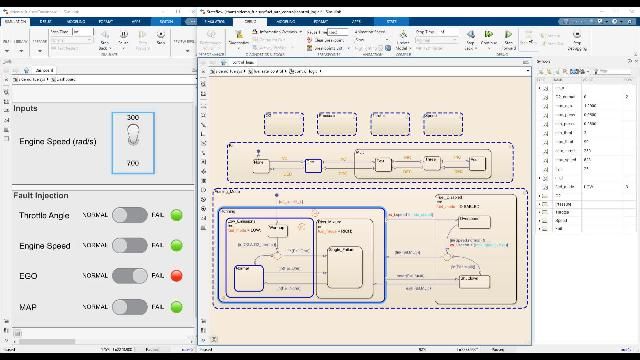

사용자는 Stateflow로 조합 및 순차 의사 결정 논리를 모델링하고, 그것을 Simulink 모델 내 블록으로서 시뮬레이션하거나 MATLAB 내 객체로서 실행할 수 있습니다. 그래픽 애니메이션을 통해 논리가 실행되는 동안에 논리를 분석하고 디버그할 수 있습니다. 편집 시 검사와 런타임 검사를 통해 설계의 일관성과 완전성을 구현 전에 보장할 수 있습니다.

상태 머신 설계

Stateflow를 사용하여 끌어서 놓기 요소와 간단한 논리문으로 상태 머신을 설계할 수 있습니다. 여러분은 Stateflow Onramp 및 교육을 수강하여 쉽게 시작할 수 있습니다.

Stateflow 차트 실행

상태 다이어그램을 실행하면 애니메이션을 통해 활성 상태와 천이가 강조 표시됩니다. 실행 중에 변수를 직접 수정하여 시스템에 미치는 영향을 시각화할 수 있습니다.

데이터 모니터링 및 분석

시뮬레이션 데이터 인스펙터는 시뮬레이션 데이터를 시각화하는 기능을 제공합니다. 이 툴을 사용하면 시스템을 모니터링하여 시스템 거동에 대한 귀중한 통찰력을 수집할 수 있습니다.

Stateflow에서의 논리 디버그

Stateflow의 디버그 기능을 통해 차트 실행을 세밀하게 순차적으로 실행할 수 있습니다. 상태 다이어그램에서 중단점을 설정하고 다양한 함수를 순차적으로 실행함으로써 예기치 못한 거동을 파악할 수 있습니다.

Stateflow 작업 스케줄링

Stateflow는 Simulink 알고리즘을 주기적 또는 연속적으로 호출하여 구성요소의 실행을 스케줄링하고 실시간 환경을 시뮬레이션할 수 있습니다.

Simulink를 사용한 설계 검증

Stateflow는 설계를 검증하고 확인하며 테스트하기 위해 다른 MathWorks 제품과 원활히 통합됩니다. 사용자는 이러한 제품들을 활용하여 설계가 요구사항을 충족하도록 하고 오류를 조기에 발견하며 품질 목표를 달성할 수 있습니다.

배포할 코드 생성

코드 생성을 통해 임베디드 시스템에서 상태 차트 논리를 구현할 수 있습니다. Stateflow는 C, C++, VHDL 및 Verilog 코드는 물론이고 PLC에 대한 Structured Text도 생성하는 워크플로를 지원합니다.