Data Converters

Simulate and analyze performance metrics of analog-to-digital and digital-to-analog data converters. Start from complete system-level models of typical ADC or DAC architectures. Modify ADC or DAC parameters until you reach your desired system specifications. Use Measurements and Testbenches to validate your design.

Blocks

Topics

- ADC Tutorial

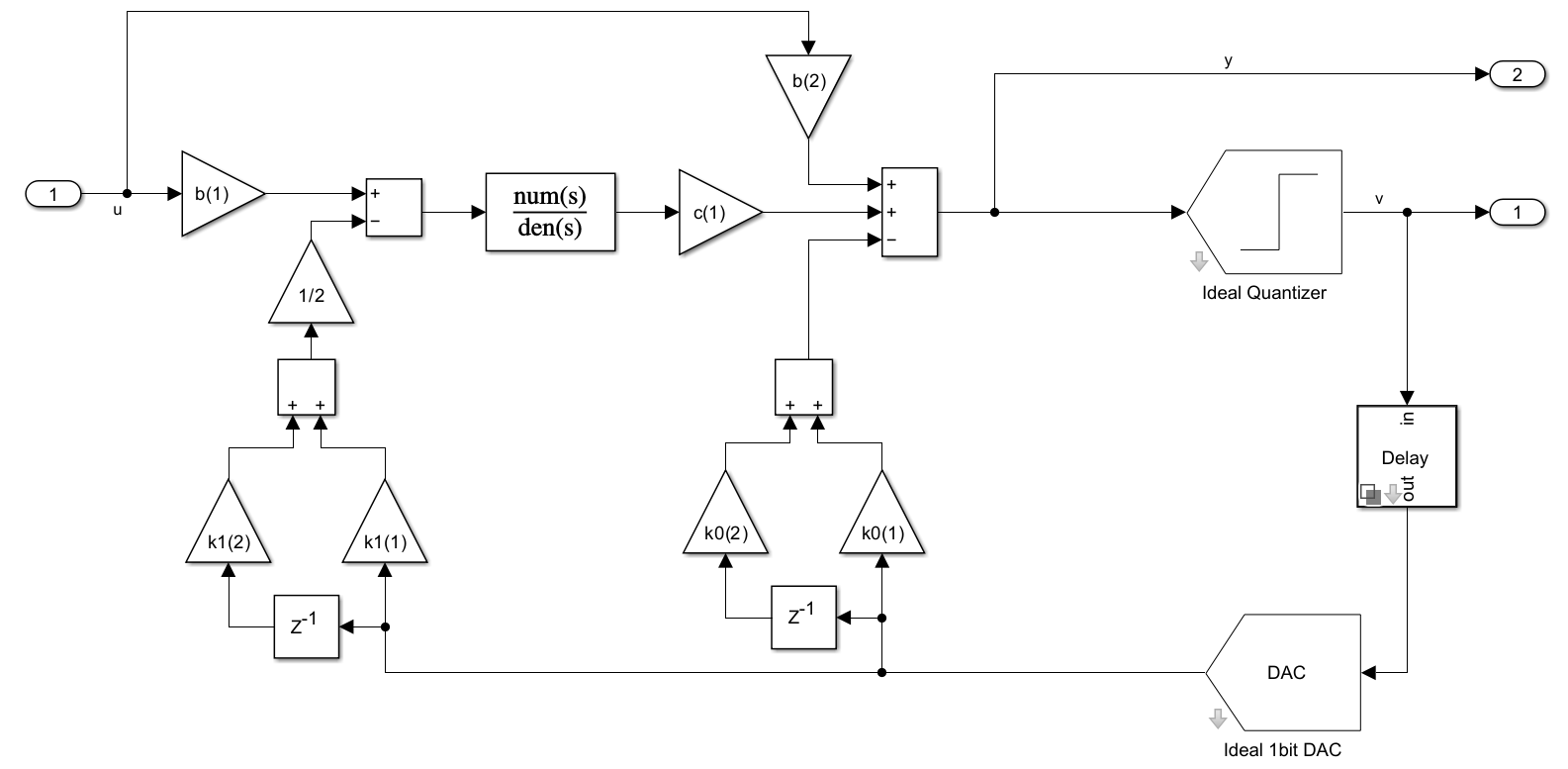

This tutorial example shows you how to design a second order Delta Sigma Analog to Digital Converter in Simulink®.

- STEP 1: System-Level Model of DSM ADC

- STEP 2: SystemVerilog Module Generation

- STEP 3: Final System-Level Model

- Compare SAR ADC to Ideal ADC

This example shows a comparison of the SAR ADC from the Mixed-Signal Blockset™ to the ideal ADC model with impairments presented in Analyzing Simple ADC with Impairments.

- Design and Evaluate SAR ADC

This example shows how to design a SAR ADC using reference architecture and validate the ADC using ADC Testbench.

- Design and Evaluate Interleaved ADC Using System Object

This example shows how to use System objects to model and evaluate the performance of an interleaved ADC.

- Effect of Metastability Impairment in Flash ADC

This example shows how to customize a flash Analog to Digital Converter (ADC) by adding the metastability probability as an impairment.

- Compare Binary Weighted DAC to Ideal DAC

This example shows a comparison of the Binary Weighted DAC from the Mixed-Signal Blockset™ to an ideal DAC model.

- Delta Sigma Modulator Data Converter with Half-Band Filter for Decimation

Use the delta sigma modulator data converter for an analog-to-digital converter application.

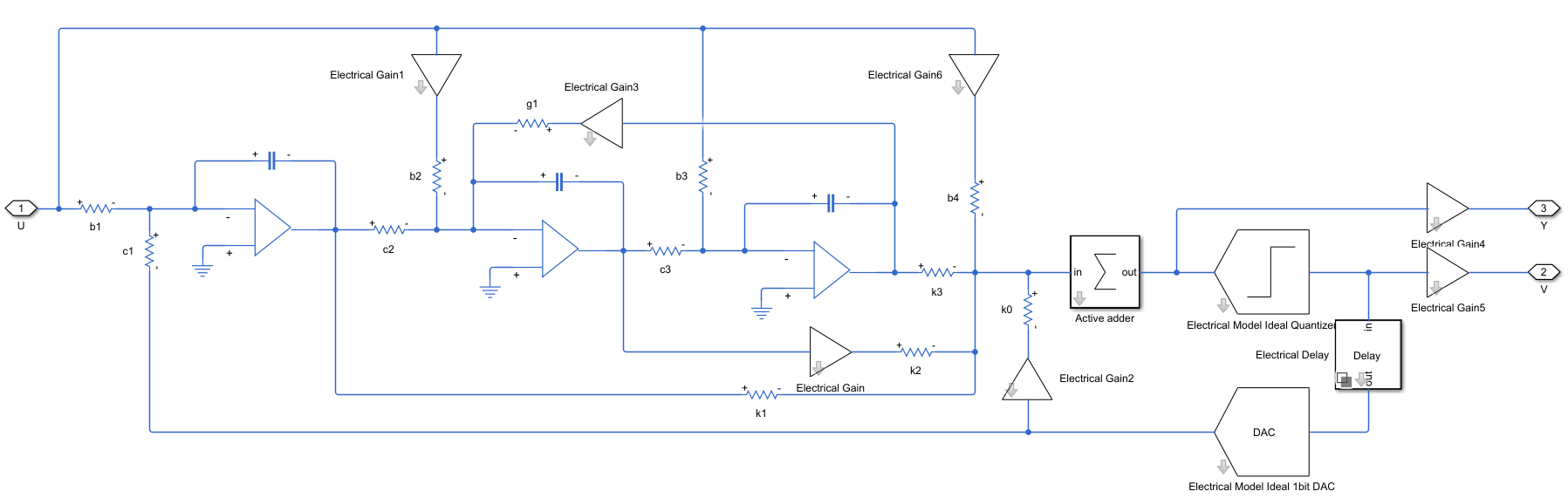

- Model Continuous-Time Delta Sigma Modulator With Inherent Anti-Aliasing Property

This example shows how to design a continuous-time delta sigma modulator (CT DSM) using the DT-CT Translation method explained in [1].