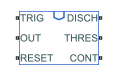

Timer

Behavioral model of a timer integrated circuit

Libraries:

Simscape /

Electrical /

Integrated Circuits

Description

The Timer block is a behavioral model of a timer integrated circuit such as the NE555.

The following figure shows the implementation structure.

The Potential divider component resistance parameter sets the values of the three resistors creating the potential divider. The two comparator inputs have infinite input resistance and zero input capacitance. The S-R Latch block provides the functionality of the set-reset latch. It includes an output capacitor and a resistor with values set to match the Propagation delay parameter value. The block models the output stage inverter using a CMOS NOT block. You define the output resistance, low-level output voltage, and high-level output voltage for the CMOS gate in the Timer block dialog box. The discharge switch approximates the NPN bipolar transistor on a real timer as a switch with defined switch on-resistance and off-resistance values.

Examples

Assumptions and Limitations

The behavior is abstracted. Results are not as accurate as a transistor-level model.

Delay in response to changing inputs depends solely upon the RC time constant of the resistor-capacitor network at the output of the latch. In practice, the delay has a more complex dependency on the device structure. Set this value based on the output-pulse rise and fall times.

The drop in output voltage is a linear function of output current. In practice, the relationship is that of a bipolar transistor push-pull pair.

The controlled switch arrangement used by the block is an approximation of an open-collector arrangement.

The power supply connects internally within the component, and the block assumes that the GND pin is grounded.

Ports

Conserving

Parameters

Extended Capabilities

Version History

Introduced in R2009b