Simplified AXI4 Master Interface

For designs that require accessing large data sets from an external memory, model your

algorithm with a simplified AXI4 Master protocol. When you run

the IP Core Generation workflow, HDL Coder™ generates an IP core with AXI4 Master interfaces.

The AXI4 Master interface can communicate between your design

and the external memory controller IP by using the AXI4 Master protocol.

Simplified AXI4 Master Protocol - Write Channel

You can use the simplified AXI4 Master protocol to map to AXI4 Master interfaces. Use the simplified AXI4 Master write protocol for a write transaction and the simplified AXI4 Master read protocol for a read transaction.

This figure shows the timing diagram for the signals that you model at the DUT input and output interfaces for an AXI4 Master write transaction.

The DUT waits for wr_ready to become high to initiate a write

request. When wr_ready becomes high, the DUT can send out the write

request. The write request consists of the Data and Write

Master to Slave

bus signals. This bus consists of wr_len,

wr_addr, and wr_valid.

wr_addr specifies the starting address that DUT wants to write

to. The wr_len signal corresponds to the number of data elements in

this write transaction. Data can be sent as long as

wr_valid is high. When wr_ready becomes low,

the DUT must stop sending data within one clock cycle, and the Data

signal becomes invalid. If the DUT continues to send data after one clock cycle, the

data is ignored.

The simplified AXI4 Master Protocol supports pipelined

requests, so it is not required to wait for the wr_complete signal to

be high before issuing a subsequent write request. The interface supports up to 16

transactions (or 16 data words) before the pipeline stalls and the

wr_ready signal goes low.

Output Signals

Model the Data and Write

Master to Slave

bus signals at the DUT output interface.

Data: The data that you want to transfer, valid each cycle of the transaction.Write Master to Slave busthat consists of:wr_addr: Starting address of the write transaction that is sampled at the first cycle of the transaction. The address is specified in bytes.wr_len: The number of data values that you want to transfer, sampled at the first cycle of the transaction. Thewr_lensignal is specified in words. Note that when Enable sample packing (last signal dimension as channel) is selected in the memory block, a word is the packed and extended data which is written to memory.wr_valid: When this control signal becomes high, it indicates that theDatasignal sampled at the output is valid.

Input Signals

Model the Write Slave to

Master bus that consists of:

wr_ready: This signal corresponds to the backpressure from the slave IP core or external memory. When this control signal goes high, it indicates that data can be sent. Whenwr_readyis low, the DUT must stop sending data within one clock cycle. You can also use thewr_readysignal to determine whether the DUT can send a second burst signal immediately after the first burst signal has been sent. Multiple burst signals are supported, which means that thewr_readysignal remains high to accept the second burst immediately after the last element of the first burst has been accepted.wr_bvalid(optional signal): Response signal from the slave IP core that you can use for diagnosis purposes. Thewr_bvalidsignal becomes high after the AXI4 interconnect accepts each burst transaction. Ifwr_lenis greater than256, the AXI4 Master write module splits the large burst signal into 256-sized bursts.wr_bvalidbecomes high for each 256-sized burst.wr_bresp(optional signal): Response signal from the slave IP core that you can use for diagnosis purposes. Use this signal with thewr_bvalidsignal.wr_complete(optional signal): Control signal that when remains high for one clock cycle indicates that the write transaction has completed. This signal asserts at the lastwr_bvalidof the burst.

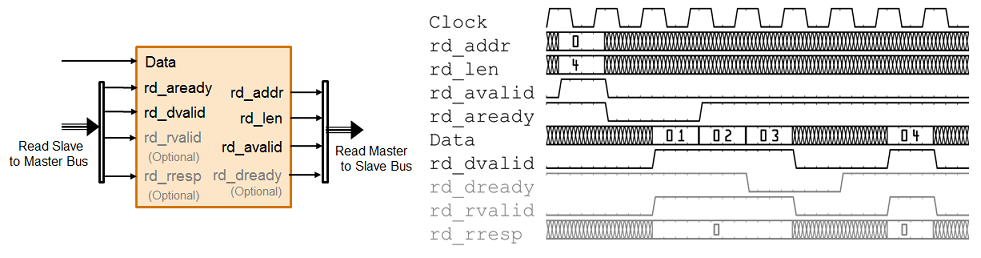

Simplified AXI4 Master Protocol - Read Channel

This figure shows the timing diagram for the signals that you model at the DUT input

and output interfaces for an AXI4 Master read transaction.

These signals include the Data, Read

Master to Slave

Bus, and Read Slave to

Master Bus.

The DUT waits for rd_aready to become high to initiate a read

request. When rd_aready is high, the DUT can send out the read

request. The read request consists of the rd_addr,

rd_len, and rd_avalid signals of the

Read Master to

Slave bus. The

slave IP or the external memory responds to the read request

by sending the Data at each clock cycle. The

rd_len signal corresponds to the number of data values to read.

The DUT can receive Data as long as rd_dvalid is

high.

Read Request

To model a read request, at the DUT output interface, model the Read

Master to Slave

bus that consists of:

rd_addr: Starting address for the read transaction that is sampled at the first cycle of the transaction. The address is specified in bytes.rd_len: The number of data values that you want to read, sampled at the first cycle of the transaction. Therd_lensignal is specified in words. Note that when Enable sample packing (last signal dimension as channel) is selected in the memory block, a word is the packed and extended data which is read from memory.rd_avalid: Control signal that specifies whether the read request is valid.

At the DUT input interface, implement the rd_aready

signal. This signal is part of the Read Slave to

Master bus and indicates when to accept read

requests. You can monitor the rd_aready signal to determine whether

the DUT can send consecutive burst requests. When rd_aready becomes

high, it indicates that the DUT can send a read request in the next clock cycle.

The simplified AXI4 Master Protocol supports pipelined

requests, so it is not required to wait for the read response to complete before issuing

a subsequent read request. The interface supports up to 4 read transactions before the

pipeline stalls and the rd_aready signal goes low.

Read Response

At the DUT input interface, model the Data and Read

Slave to Master

bus signals.

Data: The data that is returned from the read request.Read Slave to Master busthat consists of:rd_dvalid: Control signal which indicates that theDatareturned from the read request is valid.rd_rvalid(optional signal): response signal from the slave IP core that you can use for diagnosis purposes.rd_rresp(optional signal): Response signal from the slave IP core that indicates the status of the read transaction.

At the DUT output interface, you can optionally implement the

rd_dready signal. This signal is part of the Read

Master to Slave

bus and indicates when the DUT can start accepting data. By default, if

you do not map this signal to the AXI4 Master read

interface, the generated HDL IP core ties rd_dready to logic

high.

See Also

AXI4 Random Access Memory | SoC Bus Creator