PWM

입력 듀티 사이클에 대응되는 이상적인 펄스 폭 변조 신호 생성

라이브러리:

Simulink /

Discontinuities

설명

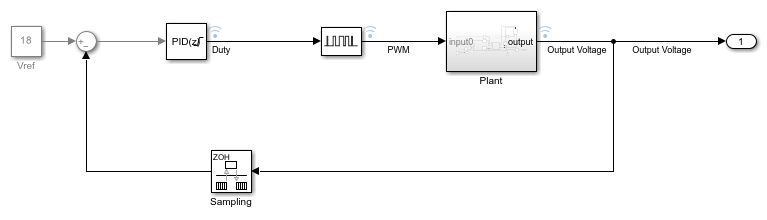

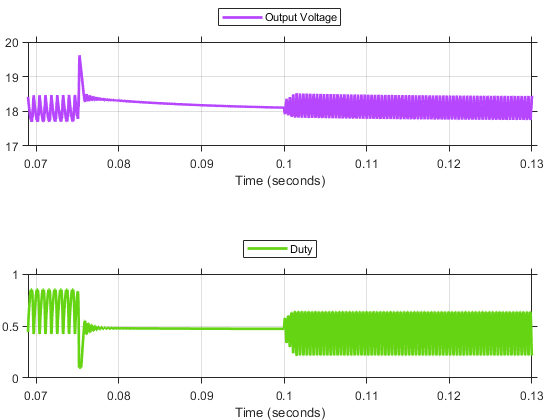

PWM 블록을 사용하여 이상적인 펄스 폭 변조 신호를 생성합니다.

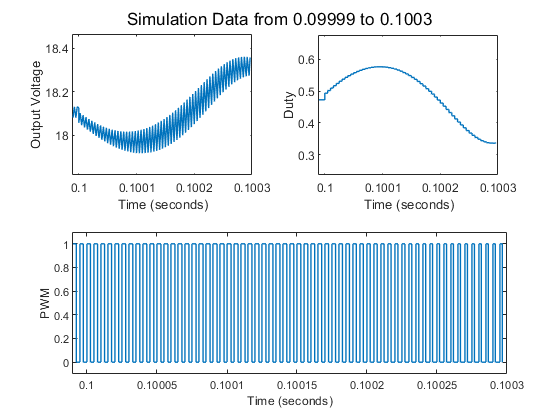

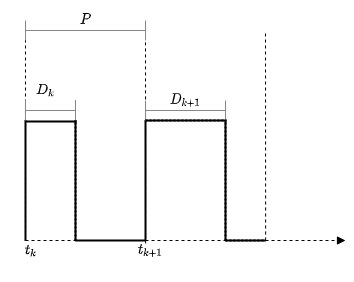

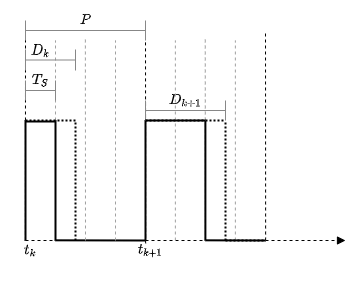

펄스 폭 변조(PWM)는 구형파를 사용하여 아날로그 신호를 인코딩하는 기법입니다. 이 인코딩은 구형파의 한 주기에서 높은 상태로 설정된 비율을 제어하여 이루어집니다. 이 비율이 PWM 신호의 듀티 사이클입니다. 변조 신호와 입력 듀티 사이클 간의 관계는 간단히 다음과 같이 설명될 수 있습니다.

여기서 ymax와 ymin은 각각 출력 신호의 상한과 하한입니다. PWM 블록의 경우 듀티 사이클은 [0,1]로 제한됩니다. 이상적인 PWM 신호는 듀티 사이클 D에 비례합니다.

예제

포트

입력

출력

파라미터

블록 특성

데이터형 |

|

직접 피드스루 |

|

다차원 신호 |

|

가변 크기 신호 |

|

영점교차 검출 |

|

알고리즘

확장 기능

버전 내역

R2020b에 개발됨