이 번역 페이지는 최신 내용을 담고 있지 않습니다. 최신 내용을 영문으로 보려면 여기를 클릭하십시오.

Bitwise Operator

입력에 대해 지정된 비트별 연산

라이브러리:

Simulink /

Logic and Bit Operations

HDL Coder /

Logic and Bit Operations

설명

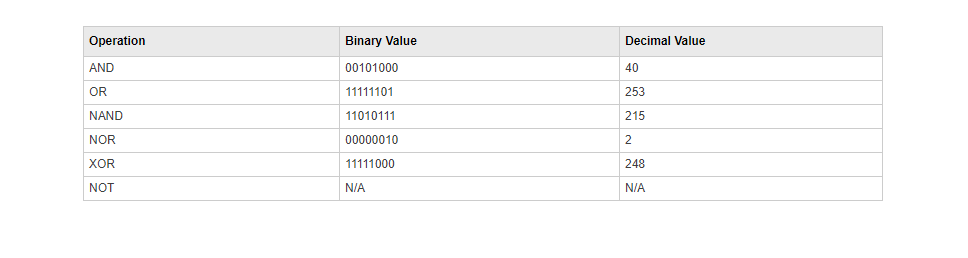

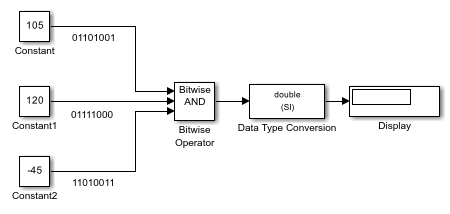

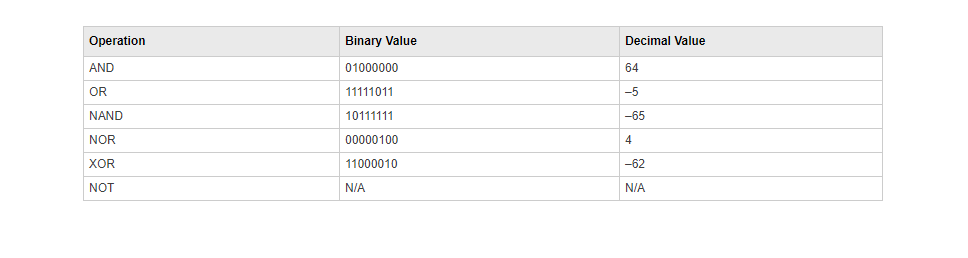

Bitwise Operator 블록은 하나 이상의 피연산자에 대해 지정된 비트별 연산을 수행합니다. Logical Operator 블록의 논리 연산과 달리, 비트별 연산은 피연산자를 단일 값이 아니라 비트로 구성된 벡터로 처리합니다.

블록 연산에 대한 제한 사항

Bitwise Operator 블록은 시프트 연산을 지원하지 않습니다. 시프트 연산의 경우 Shift Arithmetic 블록을 사용하십시오.

다중 입력 XOR 게이트로 구성된 경우 이 블록은 IEEE® Standard for Logic Elements에 따라 모듈로 2 덧셈 연산을 수행합니다.

예제

포트

입력

출력

파라미터

블록 특성

확장 기능

버전 내역

R2006a 이전에 개발됨

참고 항목

Logical Operator | Compare To Constant | Compare To Zero | Shift Arithmetic

도움말 항목

- WWV Digital Receiver - Synchronization and Detection (DSP System Toolbox)