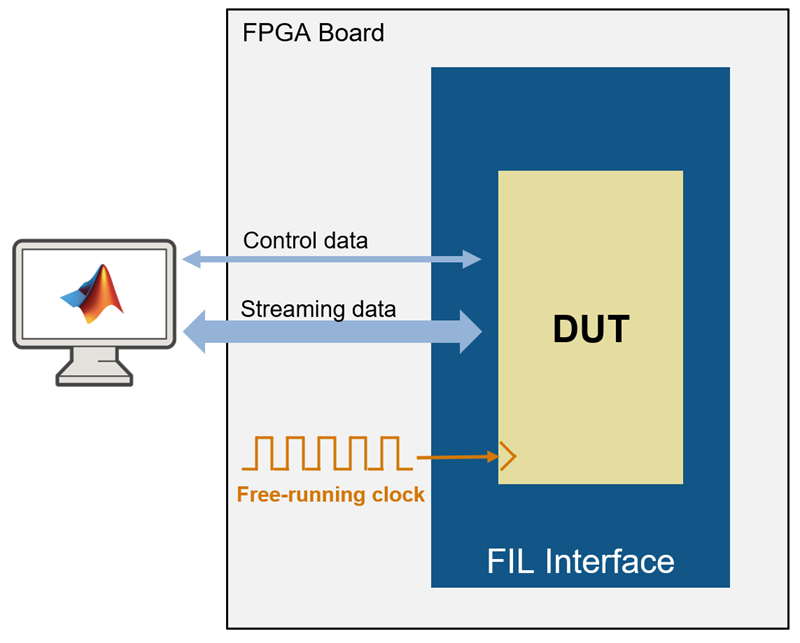

What Is Free-Running FPGA-in-the-Loop?

Introduction to Free-Running Mode

Lockstep mode and free-running mode are the two ways in which you can synchronize MATLAB® with the DUT executing on an FPGA.

Lockstep mode is the default option and it is implicit in FIL simulation. In this mode, the DUT on the FPGA operates in lockstep with MATLAB. For each step update, MATLAB must send data to all DUT input ports and receive processed data from all DUT output ports. The hardware clock toggles only upon an active data transfer. Since every clock cycle execution in the DUT corresponds to a sample step in MATLAB, lockstep mode provides cycle-accurate simulation. This level of accuracy is essential for verifying that the behavior of the DUT on the FPGA matches the simulation behavior.

In free-running mode, the DUT on the FPGA runs asynchronously with MATLAB. The hardware clock runs continuously inside the FPGA itself. Unlike lockstep mode, free-running mode requires the DUT to have data accompanied by control signals that indicate when the data is valid (see Requirements For Free-Running Mode). MATLAB can either send data or receive data in an independent manner. Although this mode does not provide cycle-accurate simulation, it can accelerate many streaming applications, as it allows the DUT to run at full speed and communicate with MATLAB only upon request.

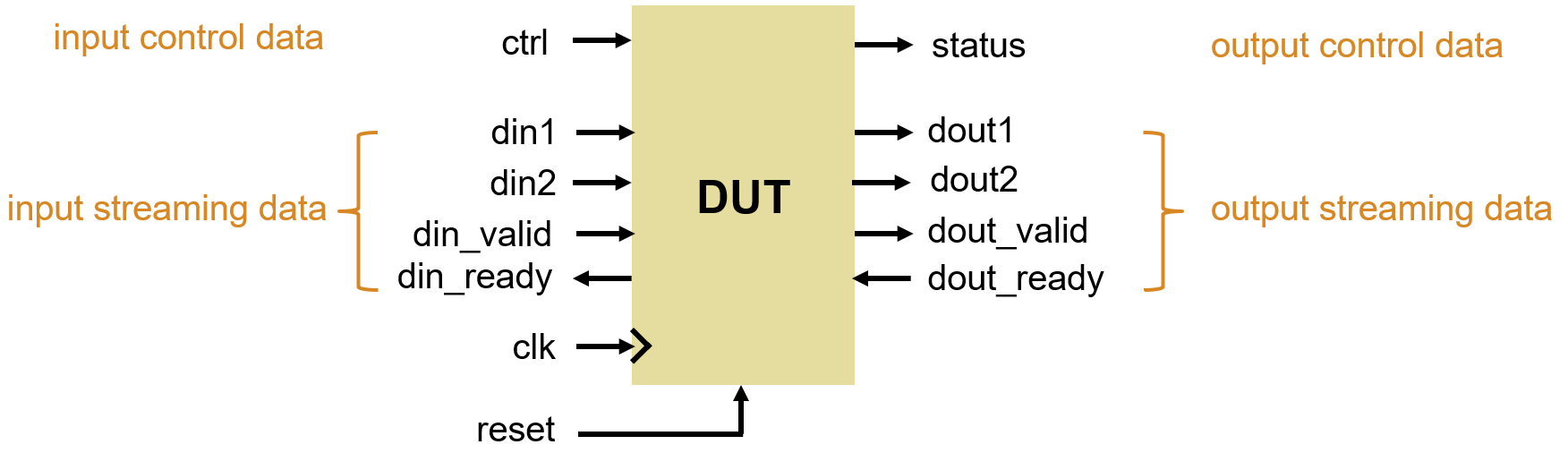

Requirements For Free-Running Mode

Free-running clock mode has the following requirements in addition to the requirements for the lockstep FIL workflow. Other than the clock, reset, and clock enable port, DUT ports are divided into four categories:

Input streaming data

Output streaming data

Input control data

Output control data

For more information about requirements for the lockstep FIL workflow, see Apply FIL System Object Requirements.

Input Streaming Data

MATLAB can send sample or frame data to the DUT streaming data ports.

An arbitrary number of streaming data ports is supported.

Arbitrary data width for each streaming data port is supported.

One data valid signal is required for all streaming data ports. The DUT registers the values of all streaming data ports whenever the data valid signal is high.

A data ready signal is optional for providing backpressure to upstream data. If your DUT does not have a ready signal, it is assumed that the DUT is always ready to accept incoming data. If your DUT has a ready signal, the valid signal immediately deasserts if the ready signal goes low.

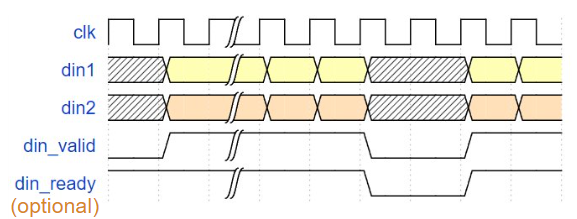

This timing diagram shows an example DUT with din1 and

din2 as streaming data ports:

Output Streaming Data

MATLAB can receive sample or frame data from the DUT streaming data ports.

An arbitrary number of streaming data ports is supported.

Arbitrary data width for each streaming data port is supported.

One data valid signal is required for all streaming data ports.

A data ready signal is optional for handling backpressure from downstream data. If the DUT has data ready signal for output streaming, the data valid signal must deassert within one clock cycle after data ready signal deasserts. If the DUT doesn't have data ready signal, a clock enable signal is required.

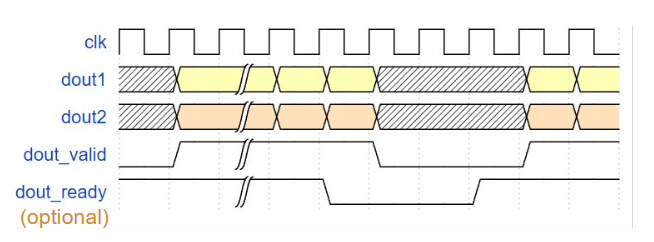

This timing diagram shows an example DUT with dout1 and

dout2 as streaming data ports:

Input Control Data

MATLAB can set the value of the DUT input control data port in a single-shot manner.

The default value of the input control data ports are all zeros. The value holds until the new value is set by MATLAB.

A data valid or data ready signal is not required.

Output Control Data

MATLAB can get the value of the DUT output control data ports in a single-shot manner.

A data valid or data ready signal is not required.

When to Use Free-Running FIL

To decide if you can benefit from free-running mode, consider the following:

Before you can accelerate your application using free-running mode, we recommended that you validate the DUT with lockstep mode, to make sure that the behavior of DUT on the FPGA matches the simulation behavior at every clock cycle.

The ports of the DUT must meet the requirements for free-running mode. See Requirements For Free-Running Mode.

Make sure your FPGA board and interface is supported. See Supported Interfaces and Boards.

Since MATLAB sends or receives streaming data only when the streaming valid signal is high, you can save bandwidth when the streaming data shows a sparse pattern, as seen in many wireless applications.

To learn more about how to accelerate your application by using free-running mode, see Accelerate NR LDPC Decoder for Streaming Data Using FPGA-in-the-Loop.

Supported Interfaces and Boards

Free-running FIL supports these interfaces:

PS Ethernet

USB Ethernet

The feature is supported on these SoC boards:

ZedBoard™

AMD® ZC702 Evaluation Kit

AMD ZC706 Evaluation Kit

AMD ZCU102 Evaluation Kit

AMD ZCU111 Evaluation Kit

AMD ZCU208 Evaluation Kit

AMD ZCU216 Evaluation Kit

AMD VCK190 Evaluation Kit

Intel Agilex® 7 SoC Development Kit