Simscape HDL Workflow Advisor Tasks

By using the Simscape HDL Workflow Advisor, you can generate an HDL implementation model.

You can then generate HDL code for the implementation model and deploy the code onto FPGA

platforms. To open the Advisor, run the sschdladvisor

function. For example:

openExample('hdlcoder/HILImplementationOfSimscapeModelOnSpeedgoatFPGAIOModulesExample',... 'supportingFile','sschdlexHalfWaveRectifierExample') sschdladvisor('sschdlexHalfWaveRectifierExample')

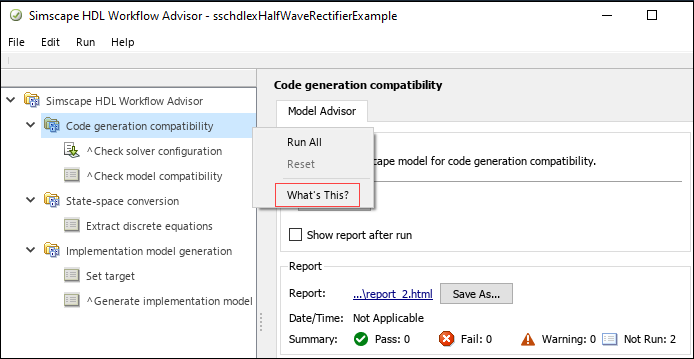

For summary information on each Simscape HDL Workflow folder or task, right-click the folder or task and select What's This?.

Simscape HDL Workflow Advisor

To convert your Simscape™ model to an HDL implementation model, the Simscape HDL Workflow Advisor contains various tasks that you can use. You can then generate code for the HDL Subsystem in the HDL implementation model. The tasks in the Simscape HDL Workflow Advisor are in these folders:

The Code generation compatibility folder contains tasks that check whether the model uses the correct solver configuration settings and reports blocks that are not compatible for HDL code generation.

The State-space conversion folder contains tasks that get the state-space parameters from your model for generating the implementation model.

The Implementation model generation folder contains tasks that generate the HDL implementation model from the state-space parameters for the specified target hardware settings.

To learn more about each folder or task, right-click the folder or task and select What's This?.

Code Generation Compatibility

The tasks in the Code generation compatibility folder check whether:

You have correctly specified the solver configuration settings and the settings are consistent across Solver Configuration (Simscape) blocks inside each network in your Simscape model.

Your model uses HDL-compatible blocks.

Check Solver Configuration

The Check solver configuration task checks whether you have specified the correct settings and the settings are consistent across Solver Configuration (Simscape) blocks inside each network in your Simscape model.

The Simscape HDL Workflow Advisor checks whether you specified these settings for all Solver Configuration (Simscape) blocks:

Use local solver is selected.

Solver type is set to

Backward Euler,Partitioning, orTrapezoidal Rule.A discrete sample time,

Ts, is specified.Use fixed-cost runtime consistency iterations selection is same (either selected or cleared).

The Nonlinear iterations value is same when Use fixed-cost runtime consistency iterations is selected.

If you did not specify these settings, the task provides a link to the Solver Configuration block in your model and the settings to modify.

Check Model Compatibility

The Check model compatibility task checks whether you use HDL-compatible blocks in your Simscape model.

If this task passes, it displays :

A message indicating that the model is switched linear.

The number of Simscape networks present in the model.

The number of algebraic and differential variables for each Simscape network with links to the related blocks in your Simscape model.

Differential variables consume a quadratic amount of multiplier resources on the target FPGA device. Algebraic variables consume a linear amount of multiplier resources. You can use this information to determine how many multiplier resources your Simscape design consumes on the FPGA device.

A message with links to the Simulink-PS Converter (Simscape) and PS-Simulink Converter (Simscape) blocks in your model if you use the default names for these blocks.

The input and output ports of the

HDL Subsystemin the implementation model use the names that you specify for the Simulink-PS Converter and PS-Simulink Converter blocks. To avoid this message, use a meaningful name for these blocks.

State-Space Conversion

Before you can generate the HDL implementation model, run the tasks in this folder to get the state-space parameters from your model. The tasks in this folder:

Simulate the Simscape model to extract the differential algebraic equations and mode-switching function.

Discretize the differential algebraic equations to generate an abstract state-space representation that represents the model in the form of linear modes.

Extract Discrete Equations

The Extract discrete equations task simulates your Simscape model and extracts the differential algebraic equations and the mode-switching function. It discretizes the differential algebraic equations and generates an abstract, discrete state-space representation of the model in the form of linear modes. Each mode is represented by a set of state-space matrices. This task gets the Simulation stop time value from the original Simscape model and displays the Discrete sample time for Simscape networks.

If this task passes, it displays the simulation stop time, number of solver iterations, number of states, inputs, outputs, modes, differential variables, and state-space representation for each Simscape network present in the model.

In the Solver Configuration block, select the Use fixed-cost runtime consistency iterations check box and specify a custom value for the number of solver iterations in the Nonlinear iterations text box. To learn more, see Using Number of Solver Iterations.

The number of modes is limited by the number of switches present in your Simscape model. The maximum number of modes possible is 2n, where n is the number of switches. All the modes that the Simscape HDL Workflow Advisor generates are executed according to the input parameters by using a switching logic. The Advisor selects a valid number of modes depending on the design of your Simscape model.

Implementation Model Generation

The tasks in the Implementation model generation folder generate an HDL implementation model from the discrete state-space representation. The implementation model represents the Simscape algorithm by using Simulink® blocks that are compatible for HDL code generation for the specified target hardware settings. If the task Generate implementation model in this folder passes, it provides a link to the generated HDL implementation model.

Set Target

In this task, you can provide the information required for target hardware settings before generating the HDL implementation model. This helps incorporate the HDL optimizations (such as setting optimal sharing factor value) required for hardware deployment. In the right pane, select a Synthesis Tool option and update Family, Device, Package, and Speed for the target hardware.

Generate Implementation Model

To generate an HDL implementation model from the discrete state-space representation,

run the Generate implementation model task. The HDL implementation

model contains an HDL Subsystem that models the state-space equations by

using the state-space parameters you get by running the tasks in the State-space

conversion folder. The HDL Subsystem block represents the

DUT for which you can generate HDL code.

Before you run this task, you can:

Use the Data type precision setting to specify whether the

HDL Subsystemin the generated implementation model stores matrix types insingle,double, orfixed-pointand computes the results in the specified data type. You can select the data type from the Data type precision drop-down list. When you selectFixed-pointdata type, you can also specify the word length in the Fixed-point word length text box. To learn more, see Data Type Precision and Numerical Accuracy.Use the Map state space parameters to RAMs setting to map the state-space parameters onto the hardware resources such as RAMs or lookup tables (LUTs). To learn more, see Map State Space Parameters to RAMs.

Select the Generate validation logic for the implementation model to generate the logic that verifies whether the generated HDL implementation model is functionally equivalent to the original Simscape model. This task generates the logic for each Simscape network present in the model. You can specify a tolerance for the numerical correctness by setting Validation logic tolerance. The Validation logic tolerance is an absolute value. For example, you can specify a tolerance value of

1e-12.Select the Share adders and multipliers option to set an optimal value of the SharingFactor for the Matrix Multiply (Product) blocks in your HDL implementation model. The optimal sharing factor value for a model is calculated based on the target details provided in the Set target task in the Implementation model generation folder of the Simscape HDL Workflow Advisor. Setting this option reduces synthesis overhead and optimizes resource utilization before generating HDL code for your model. If you do not specify target hardware or you specify a target hardware that is not supported, by default the target platform Xilinx® Vivado® Kintex®-7

xc7k325tpart is used for calculating the optimal sharing factor. For more information on supported device families and parts, see Optimal Sharing Factor Supported FPGA Device Families.

If the task passes, you see a link to the generated HDL implementation model.