Convert Integer to Vector of Bits

This example shows how to implement the Word to Bits block in a Simulink® Model that converts an integer to a vector of bits. You also generate HDL code for the model.

Simulate Model

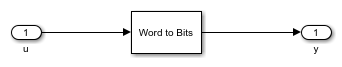

Load and open the hdlcoder_word_to_bits model. The DUT subsystem contains the Word to Bits block, which converts an integer to a vector of bits.

load_system("hdlcoder_word_to_bits"); open_system("hdlcoder_word_to_bits/DUT");

Simulate the hdlcoder_word_to_bits model. The input is an integer with a value of 72. The block uses maximum word length of 8 to determine the output vector size. The output is a binary representation of 72. The block treats first element of the output vector as the least significant bit (LSB) of the output.

sim('hdlcoder_word_to_bits');

Generate HDL code

You can generate the HDL code for a model by using HDL Coder™. To generate HDL code for DUT subsystem, run this makehdl command:

makehdl("hdlcoder_word_to_bits/DUT")