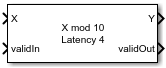

Modulo by Constant HDL Optimized

Perform mod operation with a constant denominator and generate optimized HDL code

Libraries:

Fixed-Point Designer HDL Support /

Math Operations

Description

The Modulo by Constant HDL Optimized block performs the modulo operation (remainder after division) with a constant denominator using an HDL-optimized architecture with cycle-true latency.

The Modulo by Constant block uses an algorithm that is functionally similar to a Barrett Reduction. The division operation is computed via a multiplication by inverse, which generally results in better performance on embedded systems.

Examples

Implement HDL Optimized Modulo by Constant

How to use the Modulo by Constant HDL Optimized block.

Ports

Input

Dividend, specified as a real-valued scalar, vector, matrix, or multidimensional array.

If X is a fixed-point data type, it must use binary-point scaling. Slope-bias representation is not supported for fixed-point data types.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | fixed point

Whether input is valid, specified as a Boolean scalar. This control signal

indicates when the data from the X input port is valid. When this

value is 1 (true), the block captures the value

on the X input port. When this value is 0

(false), the block ignores the input samples.

Data Types: Boolean

Output

Result of modulus operation, returned as a scalar, vector, matrix, or multidimensional array.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | fixed point

Whether the output data is valid, returned as a Boolean scalar. When the value of

this control signal is 1 (true), the block has

successfully computed the output Y. When this value is

0 (false), the output data is not

valid.

Data Types: Boolean

Parameters

Divisor to use for the modulus operation, specified as a positive, real-valued, finite scalar, vector, matrix, or multidimensional array.

Programmatic Use

Block Parameter:

Denominator |

| Type: character vector |

| Values: MATLAB® expression that evaluates to a positive, real-valued, finite fixed point or numeric value |

Data Types:

single | double | int8 |

int16 | int32 | int64 |

uint8 | uint16 | uint32 |

uint64 | Boolean | fixed

point |

Default:

'10' |

Algorithms

The modulo operation,

is an important building block for many mathematical algorithms. However, this formula for X mod D is computationally inefficient for fixed-point and integer inputs. Many embedded processors lack instructions for integer division. Those that do have them require many clock cycles to compute the answer. Division is also inefficient in commercially-available FPGAs, whose arithmetic circuits are designed for efficient multiplication, addition, and subtraction. Finally, for fixed-point modulo operations, it is difficult to optimize the word length of internal data types used for the calculation because the division operation is unbounded, even for small-wordlength inputs.

The denominator in the modulo problem is a compile-time constant, so the block can compute the floored division by using a multiplication followed by a cast. Rewriting the division operation as

shows this. The constant is calculated to the precision necessary to maintain both accuracy and computational efficiency. The cast that follows discards any fractional bits, which is an efficient operation on both microprocessors and FPGAs.

The Modulo by Constant block uses an algorithm that is functionally similar to a Barrett Reduction. The division operation is computed via a multiplication by inverse, which generally results in better performance on embedded systems.

The Modulo by Constant HDL Optimized block performs the modulo operation (remainder after division) with a constant denominator using an HDL-optimized architecture with cycle-true latency.

The latency is:

0whenDenominatoris a power of24otherwise

Extended Capabilities

Slope-bias representation is not supported for fixed-point data types.

HDL Coder™ provides additional configuration options that affect HDL implementation and synthesized logic.

This block has one default HDL architecture.

| General | |

|---|---|

| ConstrainedOutputPipeline | Number of registers to place at

the outputs by moving existing delays within your design. Distributed

pipelining does not redistribute these registers. The default is

|

| InputPipeline | Number of input pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| OutputPipeline | Number of output pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

Slope-bias representation is not supported for fixed-point data types.

Version History

Introduced in R2021aThe latency of the Modulo by Constant HDL Optimized block has been reduced from 9 clock cycles to 4 clock cycles.

The Modulo by Constant HDL Optimized block now supports vector and matrix inputs.

The Modulo by Constant HDL Optimized block is supported for use inside a For Each Subsystem block.

See Also

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

웹사이트 선택

번역된 콘텐츠를 보고 지역별 이벤트와 혜택을 살펴보려면 웹사이트를 선택하십시오. 현재 계신 지역에 따라 다음 웹사이트를 권장합니다:

또한 다음 목록에서 웹사이트를 선택하실 수도 있습니다.

사이트 성능 최적화 방법

최고의 사이트 성능을 위해 중국 사이트(중국어 또는 영어)를 선택하십시오. 현재 계신 지역에서는 다른 국가의 MathWorks 사이트 방문이 최적화되지 않았습니다.

미주

- América Latina (Español)

- Canada (English)

- United States (English)

유럽

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)