DSP HDL IP Designer

Configure and generate HDL code for digital signal processing IP cores

Since R2024b

Description

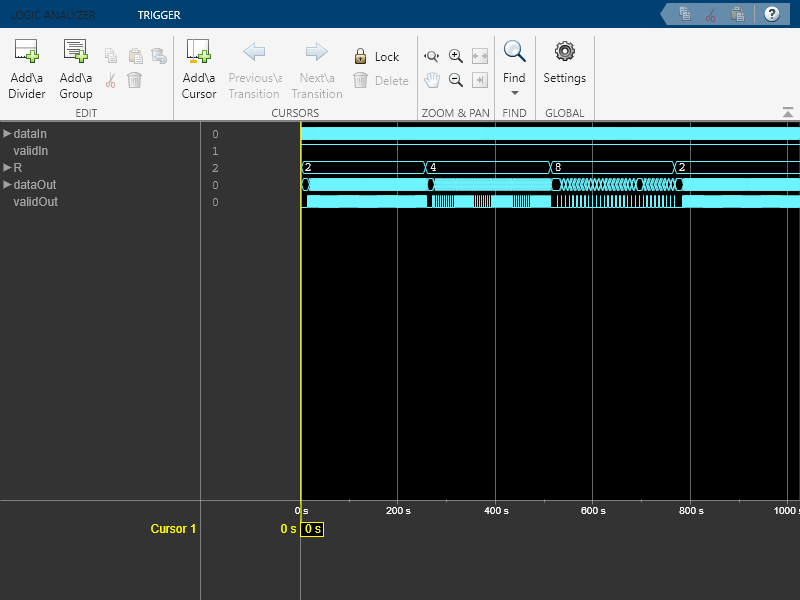

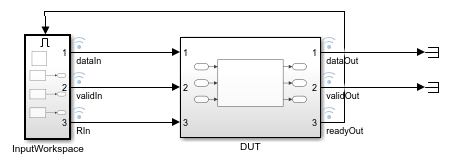

Use the DSP HDL IP Designer app to select a digital signal processing (DSP) algorithm and configure parameters and input stimulus. Then, generate HDL code and a testbench to verify the behavior of your design.

The app enables you to select and configure hardware-optimized algorithms and generate HDL code for those algorithms. The app provides algorithms that have streaming data interfaces and hardware-friendly control signals. The algorithms can use frame-based input and parallel operations to achieve gigasamples-per-second (GSPS) data rates, also called super sample rates. You can change the algorithm parameters to explore and generate different hardware implementations. The app supports HDL code generation and optional generation of an HDL testbench. To generate HDL code and testbench you must have the HDL Coder™ product. If you have the HDL Verifier™ product, you can generate a cosimulation testbench or a DPI component for your algorithm.

To get started, see Generate and Verify HDL Code with DSP HDL IP Designer App.

You can save and restore your IP design session by using the buttons on the toolbar. When you save a session, the app creates a

.matfile with the name you specify. (since R2025a)You can configure and generate HDL code for one algorithm at a time. Select your algorithm from the IP Blocks gallery.

Click the Input Stimulus block to configure input data signals. The dimensions and data types of these values define your HDL interface, and the generated testbench applies these values to your algorithm. You do not have to specify stimulus for input control signals. The app provides default values for each input port, assigned as fields in the

testbenchstructure. For help creating input stimulus, see Setting Input Stimulus.When you design biquad or discrete FIR filters, you can use the Analyze button in the toolbar to open the Filter Analyzer app and visualize the characteristics of the filter. (since R2025a)

To configure HDL code generation options, including enabling generation of an HDL simulator testbench, click Configure HDL. For more information about the available options, see Parameters. Then, to generate code, click Generate HDL. After you generate HDL code, you can see output log messages on the Console tab and a hardware resources estimate on the Resources tab. You must have the HDL Coder product to generate HDL code.

To generate a cosimulation testbench, set options in the EDA Scripts and Cosimulation tab of the Configure HDL menu. For more information about the available options, see EDA Scripts and Cosimulation. You must have the HDL Verifier product to use the cosimulation testbench feature.

To generate a SystemVerilog DPI component, select Generate DPI Component from the Generate HDL menu. You can integrate this component into your HDL simulation as a behavioral model. You must have the HDL Verifier product to use the Generate DPI Component feature.

You can export your designs as either a MATLAB® script file or a Simulink® model that includes your configured algorithm and input stimulus, and simulates your algorithm. For more details see Export Algorithm to MATLAB and Export Algorithm to Simulink. (since R2025a)

Open the DSP HDL IP Designer App

MATLAB Toolstrip: On the Apps tab, under Signal Processing and Audio, click the app icon.

MATLAB command prompt: Enter

dsphdlIPDesigner.MATLAB command prompt: Load a preconfigured System object™ into the app by entering

dsphdlIPDesigner(ObjVariable). For which objects are supported, see Generate HDL for Preconfigured Algorithm with DSP HDL IP Designer App. (since R2025a)Filter Designer (Signal Processing Toolbox) app: Under the Export menu, select Export to DSP HDL IP Designer. For which filters are supported, see Generate HDL for Preconfigured Algorithm with DSP HDL IP Designer App. (since R2026a)

Examples

Related Examples

Parameters

Setting Input Stimulus

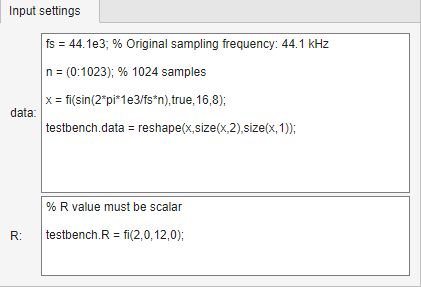

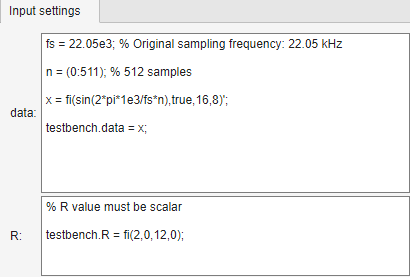

After you select your algorithm and set its parameters, click the Input

Stimulus block to configure input data signals. The dimensions and data types of

these values define your HDL interface, and the generated testbench applies these values to

your algorithm. You do not have to specify stimulus for input control signals. The app

provides default values for each input port, assigned as fields in the

testbench structure. You must use the same field names as the default

stimulus.

The testbench.data input must be a 1-D or 3-D matrix in the data type

that you want your HDL IP core to use. A 1-D matrix represents a stream of data samples over

time. A 3-D matrix represents number of input samples per

cycle-by-number of data channels-by-data samples

over time. For example:

testbench.data = uint8(1:1:1024)is a 1-D matrix that represents 1024uint8input samples with one input sample per cycle.testbench.data = reshape(uint8(1:1:1024),4,1,[])is a 3-D matrix, with dimensions 4-by-1-by-256, that represents an input frame size of 4 samples per cycle for 256 cycles.testbench.data = reshape(uint8(1:1:1024),1,2,[])is a 3-D matrix, with dimensions 1-by-2-by-512, that represents 2 channels, each with one input sample per cycle, for 512 cycles. Multichannel filters do not support frame-based input.

Other input signals can be scalars or vectors. For example:

testbench.coeff = fi(fir1(17,0.1),1,16)is a single set of filter coefficients, specified as a 1-by-18 vector of 16-bit fixed-point values.testbench.R = fi(2,0,12,0)is a decimation factor input, specified as a scalar 12-bit integer value.

Some algorithms have a dependency between the algorithm properties and the ports and dimensions of the input stimulus. Configure the properties and input stimulus to match before clicking Apply. The Apply action incorporates any changes from properties and from input stimulus.

You can enter code that generates your input values. Because this code is also used in HDL code generation, it must follow the same limitations as in the testbench file specified for MATLAB to HDL code generation. See Using Test Benches With HDL and HLS Code Generation (HDL Coder).

The input stimulus code cannot directly access workspace variables. To make use of

existing workspace data, call

evalin('base',<expression>).