HDL Verifier를 사용하면 FPGA, ASIC, SoC에 대한 VHDL® 및 Verilog® 설계를 테스트하고 검증할 수 있습니다. Siemens® Questa™ 또는 ModelSim™, Cadence® Xcelium® 및 AMD® Vivado® 시뮬레이터를 사용한 연동 시뮬레이션을 통해 MATLAB 또는 Simulink에서 실행되는 테스트벤치로 RTL을 검증할 수 있습니다. 동일한 테스트벤치를 FPGA 개발 보드와 함께 재사용하여 하드웨어 구현물을 검증할 수 있습니다.

HDL Verifier는 RTL 테스트벤치 및 완전한 UVM(범용 검증 방법론) 환경을 위한 SystemVerilog 검증 모델을 생성합니다. 이러한 모델은 SystemVerilog Direct Programming Interface(DPI)를 통해 Questa, Xcelium, Vivado 및 Synopsys® VCS®에서 네이티브 모델로 실행됩니다.

HDL Verifier는 MATLAB에서 AMD, Intel®, Microchip 보드의 구현물을 디버그하고 테스트하는 툴을 제공합니다. 설계에 프로브를 삽입하고 트리거 조건을 설정하여 내부 신호를 MATLAB에 업로드해서 시각화하고 분석할 수 있습니다.

RTL 검증

HDL 시뮬레이터와의 연동 시뮬레이션을 통해 MATLAB 및 Simulink 테스트벤치로 ASIC 또는 FPGA용 HDL 코드를 검증할 수 있습니다. 단위 수준 또는 칩 수준 테스트에 사용되는 검증 환경을 만들기 위해 SystemVerilog 테스트벤치를 생성할 수 있습니다.

FPGA 프로토타이핑, 검증, 테스트

FPGA-in-the-Loop 테스트를 사용하여 FPGA 개발 보드에서 하드웨어 기반 검증을 수행할 수 있습니다. MATLAB에서 하드웨어 디버깅, 제어 테스트를 위해 설계 내 내부 신호를 탐지할 수 있습니다.

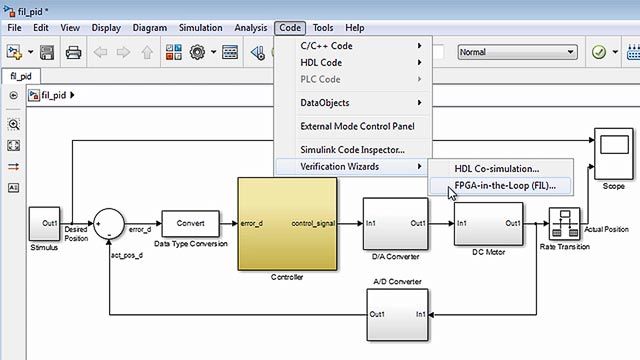

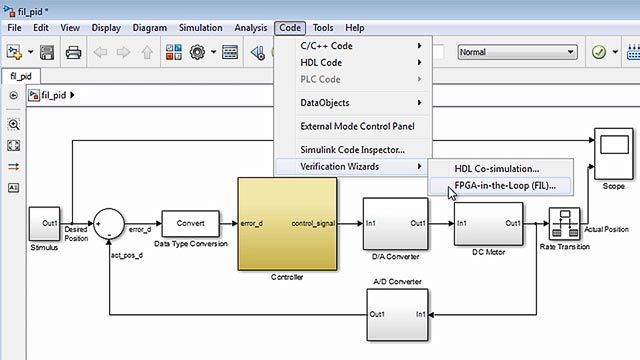

FPGA-in-the-Loop

MATLAB 및 Simulink 테스트벤치를 사용하여 FPGA 보드에서 실행되는 HDL 구현을 테스트할 수 있습니다. 이더넷, JTAG 또는 PCI Express®를 통해 호스트 컴퓨터를 AMD, Intel, Microchip FPGA 보드에 자동으로 연결할 수 있습니다.

SystemVerilog DPI 생성

ASIC Testbench를 사용하여 MATLAB 함수 또는 Simulink 서브시스템을 VCS, Xcelium, ModelSim 또는 Questa 등의 기능 검증 환경에서 사용할 수 있는 SystemVerilog DPI 컴포넌트로 생성해낼 수 있습니다.

MATLAB: 문서 | 예제

UVM 환경 생성

ASIC Testbench를 사용하여 Simulink 모델로부터 완전한 UVM(범용 검증 방법론) 테스트벤치를 생성할 수 있습니다. UVM 시퀀스, 스코어보드, 프리딕터를 생성하고 이를 Questa, Xcelium, VCS 또는 Vivado 시뮬레이터에 기반한 프로덕션 테스트벤치에 통합할 수 있습니다.

SystemC TLM 2.0 호환 트랜잭션 수준 모델 생성

ASIC Testbench를 사용해서 TLM 2.0 인터페이스를 갖춘 SystemC 가상 프로토타입 모델을 생성하여 가상 플랫폼 시뮬레이션에서 사용할 수 있습니다. TLM 생성기를 사용하여 Simulink와 생성된 TLM 구성요소 간의 매핑 정보가 담긴 IP-XACT 파일을 만들 수 있습니다.

제품 관련 자료:

“Simulink를 통해 우리는 생산 UVM 테스트벤치, 테스트 시퀀스 및 스코어보드를 직접 작성하는 시간을 약 50%나 단축할 수 있었고, 이를 통해 획기적 혁신을 위한 응용 사례에 집중할 시간이 늘어났습니다. 자동차 응용 사례를 위해 설계된 우리 ASIC은 생산 검증 단계에서 UVM에 크게 의존하는데, MATLAB 및 Simulink를 통해 정말 지루했던 이런 소자에 대한 알고리즘 개발 작업을 간소화할 수 있었습니다.”

Khalid Chishti, Allegro MicroSystems