OTAVA DTRX2

Libraries:

SoC Blockset Support Package for AMD FPGA and SoC Devices /

RFSoC /

ZCU208

Description

Add-On Required: This feature requires the SoC Blockset Support Package for AMD FPGA and SoC Devices add-on.

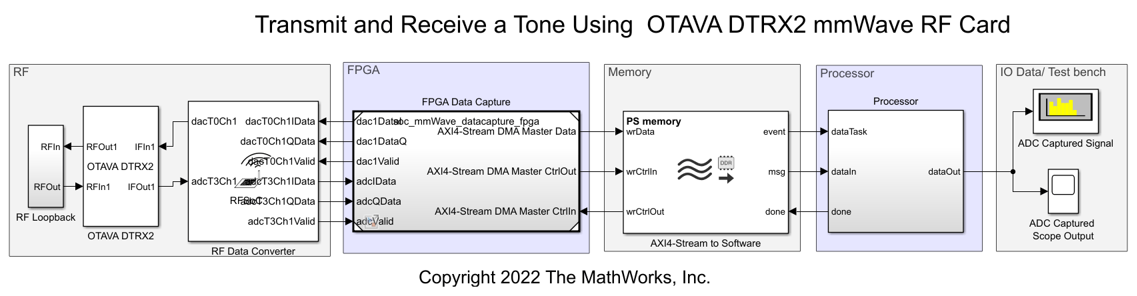

The OTAVA DTRX2 block integrates the OTAVA DTRX2 mmWave radio card with the Xilinx® Zynq® UltraScale+™ RFSoC ZCU208 Evaluation Kit. The block provides an RF front-end interface in the millimeter-wave (mmWave) frequency band to implement your RF applications on the ZCU208 board.

The block supports the mmWave frequency band in the 19 to 31 GHz range. Use this block to target applications in 5G, radar, and satellite communications in Ka or Ku band.

The block accepts a vector of N samples through the

IFInx ports and outputs 16-bit samples as a column

vector with a length in the range [1, N] through the

RFOutx ports. N is the number of

samples per clock cycle and x is 1 or 2. The block accepts 16-bit

samples as a column vector with a length in the range [1, N] through the

RFInx ports and outputs a vector of

N samples through the IFOutx

ports based on the value of N.

In generation, the SoC Builder tool maps the control path interface for the configuration of the DTRX2 radio card on the hardware.

The block supports a maximum of two transmit (TX) and two receive (RX) channels. These channels correspond to the TX and RX channels of the DTRX2 radio card.

| Block Channel | DTRX2 Radio Card Channel |

|---|---|

| IFIn1 - RFOut1 | TX1 |

| IFIn2 - RFOut2 | TX2 |

| RFIn1 - IFOut1 | RX1 |

| RFIn2 - IFOut2 | RX2 |

To integrate the OTAVA DTRX2 block with the RF Data Converter block, follow these instructions.

Connect TX1 with DAC 1 in Tile 0.

Connect TX2 with DAC 0 in Tile 0.

Connect RX1 with ADC 1 in Tile 3.

Connect RX2 with ADC 0 in Tile 3.

Note

Do not target any signal to the DTRX2 radio card when the card power switch is off. Turn the power switch on before targeting the card.

For reference clock spurious mitigation, use a 10 dB coaxial attenuator or a low-pass filter with a cutoff value greater than 122.88 MHz between the CLK104 output and the REF_CLK_IN input of the DTRX2 radio card.

Terminate all unused RF channels input and output connectors of the DTRX2 radio card with 50 ohms 2.92 mm terminations.

For detailed instructions on setting up and using the mmWave radio card, see Wideband mmWave Radio Dev Kit for RFSoC Gen-3 on the Avnet® website.

Examples

Limitations

In the hardware setup, set Hardware Board to

Xilinx Zynq UltraScale+ RFSoC ZCU208 Evaluation Kitand set Add-on Card toNone.This block supports SoC generation using the SoC Builder tool. This block does not support the IP core generation workflow. For more information on workflows, see SoC Generation Workflows.

Ports

Input

Output

Parameters

Extended Capabilities

Version History

Introduced in R2023a