Requirements Table

Libraries:

Requirements Toolbox

Description

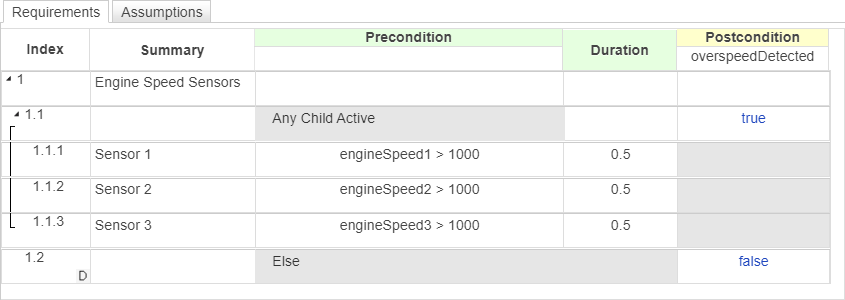

The Requirements Table block models formal requirements. The block first evaluates the conditions in the Precondition column. If the conditions are satisfied, the block checks if other simulation data meets the conditions in the Postcondition column or executes the actions in the Action column. For more information, see Use a Requirements Table Block to Create Formal Requirements.

You can constrain requirements based on the physical limitations of your model by defining assumptions in the Assumptions tab. See Add Assumptions to Requirements.

You can configure this block only if you have Requirements Toolbox™.

Examples

Model Dice Game Rules Using a Requirements Table Block

Use a Requirements Table block to model the rules and the game outcome associated with a dice game.

- Since R2022a

- Open Model

Analyze Formal Requirements of an Electric Vehicle Charger Locking Mechanism

Use a Requirements Table block and Simulink® Design Verifier™ to construct, analyze, and update formal requirements of an electric vehicle charging station locking mechanism.

- Since R2022a

- Open Live Script

Define Formal Requirements with a Duration

Define formal requirements that use a duration.

- Since R2022a

- Open Live Script

Use Specification Models for Requirements-Based Testing

Follow a systematic approach to verify your design model against requirements.

- Since R2022b

- Open Live Script

Prove Properties with Requirements Table Blocks

Use a Requirements Table block and Simulink Design Verifier to prove properties of a model.

- Since R2023a

- Open Model

Ports

Input

Input data, specified as a real-valued scalar, vector, or matrix. Each input data that you define has a corresponding input port.

Dependencies

To create input ports, open the block and create input data in the Symbols pane. See Define Data in Requirements Table Blocks.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | string | fixed point | enumerated | bus

Output

Output data, specified as a real-valued scalar, vector, or matrix. Each output data that you define has a corresponding output port.

Dependencies

To create output ports, open the block and create output data in the Symbols pane. See Define Data in Requirements Table Blocks.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | string | fixed point | enumerated | bus

Parameters

To edit the block parameters interactively:

Use the Property Inspector. From the Simulink Toolstrip, on the Simulation tab, in the Prepare gallery, select Property Inspector.

Use the Table Properties window. Open the block. Then, in the Simulation tab, in the Prepare section, click Table Properties.

Note

Requirements Table blocks also have Subsystem (Simulink) block parameters that you can access by right-clicking the block and

clicking the Block Parameters button ![]() . However, updating these block parameters is not

recommended.

. However, updating these block parameters is not

recommended.

Specify the method for activating the Requirements Table block as one of these values:

Inherited— Input from the Simulink model activates the Requirements Table block.If you define input data, the Requirements Table block samples at the rate of the fastest input data. If you do not define input data, the Requirements Table block samples at the rate defined by the execution behavior of the parent subsystem.

Discrete— Sample the Requirements Table block by using the rate you specify in the Sample time parameter of the Requirements Table block. The Requirements Table block generates an implicit event at regular time intervals that correspond to the specified rate. Other blocks in the model can have different sample times.

Specify the time interval at which the Requirements Table block activates during simulation. The default value indicates that the block inherits the sample time from Simulink. This property uses the same format that you use in Simulink. For more information on specifying sample time, see Specify Sample Time (Simulink).

Do not use the Sample Time parameter in the Subsystem block parameters. Instead, use the Table Properties window.

Dependencies

To enable this parameter, set the block parameter Update

method to Discrete.

Specify whether the data in the Requirements Table block saturates on integer overflow as one of these values:

on— The block saturates an integer by setting it to the maximum positive or negative value allowed by the word size. This setting matches MATLAB® behavior.off— The block wraps the value.

For more information, see Saturation and Wrapping (Fixed-Point Designer).

Specify whether the Requirements Table block supports input and

output data that varies in dimension during simulation. When this parameter is

on, you can define variable-size outputs by enabling the

Variable size property on output data. For more information, see

Variable size.

Specify whether the block can use data with Scope set to

Output in preconditions. If you disable this parameter, the

block highlights the cell and displays an alert icon ![]() in preconditions that use output data, unless the data

is an input argument of

in preconditions that use output data, unless the data

is an input argument of getPrevious. However, if getPrevious

attempts to return the value of the data at a time step when it is not defined,

getPrevious returns undefined behavior.

Tips

When you use output data in preconditions, you may encounter read-before-write issues in your requirements during simulation. To resolve these issues, specify your requirements in order. For more information, see Detect Read-Before-Write Issues and Leverage Evaluation Order of Formal Requirements.

Fixed-point properties

Specify the default fimath object properties for the

Requirements Table block as one of these values:

Same as MATLAB— The block uses the samefimathobject properties as the current defaultfimathobject. The text box is dimmed and displays the current globalfimathobject.Specify other— Specify your ownfimathobject in the text box one of two ways:Construct the

fimathobject inside the text box.Construct the

fimathobject in the MATLAB or model workspace and then enter its variable name in the text box. If you use this option and plan to share your model with others, define the variable in the model workspace.

For more information on

fimathobjects, see fimath Object Construction (Fixed-Point Designer).

Tips

The

fimathobject of a Requirements Table block behaves as aglobalfimath(Fixed-Point Designer) for the contents of the block. The block associates thefimathobject properties in this parameter with the fixed-point and integer input signals to the block that you choose to treat asfiobjects. Constructingfiobjects in the Requirements Table block introduces additional considerations.If no

fimathobject is associated with afiobject when it is constructed, then theficonstructor uses the defaultfimathobject settings regardless of the properties in Requirements Table fimath. If you perform operations on thefiobject after it is constructed, the object adopts the properties in Requirements Table fimath.If you specify a

fimathobject in theficonstructor, then theficonstructor obeys thatfimathobject when quantizing the value.fimathsettings not specified in theficonstructor use the specified properties in Requirements Table fimath.

Extended Capabilities

Actual data type or capability support depends on block implementation.

Actual data type or capability support depends on block implementation.

HDL Coder™ provides additional configuration options for HDL implementation and synthesized logic.

This block has one default HDL architecture.

| ConstMultiplierOptimization | Canonical signed digit (CSD) or factored CSD optimization. The

default is |

| ConstrainedOutputPipeline | Number of registers to place at

the outputs by moving existing delays within your design. Distributed

pipelining does not redistribute these registers. The default is

|

| DistributedPipelining | Pipeline register distribution,

or register retiming. The default is |

| GuardIndexVariables | Specify whether to hoist array indices out of conditional statements or

not. When you enable certain optimizations such as RAM Mapping, loop streaming,

sharing, and so on, expressions are moved out of the array indices. A temporary

variable is created for the expression that might result in an index out-of-

bounds error during simulation. The default is |

| InputPipeline | Number of input pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| InstantiateFunctions | Generate a VHDL® |

| LoopOptimization | Unroll, stream, or do not optimize loops. The default is |

| MapPersistentVarsToRAM | Map persistent arrays to RAM. The default is |

| OutputPipeline | Number of output pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| ResetType | Suppress reset logic generation. The default is |

| SharingFactor | Number of functionally equivalent resources to map to a single shared resource. The default is 0. See also Resource Sharing (HDL Coder). |

The block participates in these HDL optimizations to optimize the speed, and area.

Speed and Area Optimization

| Optimization | Description |

|---|---|

| Specify Distributed Pipelining Settings (HDL Coder) | Distributed pipelining, or register retiming, is a speed optimization that moves existing delays in a design to reduce the critical path while preserving functional behavior. |

| Resource Sharing (HDL Coder) | Resource sharing is an area optimization in which HDL Coder identifies multiple functionally equivalent resources and replaces them with a single resource. |

| Understand Delay Balancing in HDL Coder (HDL Coder) | When optimizations or block implementation options introduce delays along the critical path in a model, Delay Balancing detects introduction of new delays along one path, and then inserts matching delays on the other paths. |

| Clock-Rate Pipelining (HDL Coder) | Clock-rate pipelining is an optimization framework in HDL Coder that allows other speed and area optimizations to introduce latency at the clock rate. |

| Specify Adaptive Pipelining Settings (HDL Coder) | Adaptive pipelining optimization creates patterns or combination of blocks with registers that can improve the achievable clock frequency and reduce the area usage on the FPGA boards by inserting pipeline registers to the blocks in your design. |

| Critical Path Estimation (HDL Coder) | To quickly identify the most likely critical path in your design, use Critical Path Estimation. Critical path estimation speeds up the iterative process of finding the critical path. To know blocks that are characterized in critical path estimation, see Characterized Blocks (HDL Coder). |

When you apply optimizations, the block has these limitations:

HDL optimizations are not supported for the block that has Trigger port.

Actual data type or capability support depends on block implementation.

Version History

Introduced in R2022aYou can now create and manipulate string data in Requirements Table blocks. The string data type is compatible with strings in MATLAB and Simulink.

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

웹사이트 선택

번역된 콘텐츠를 보고 지역별 이벤트와 혜택을 살펴보려면 웹사이트를 선택하십시오. 현재 계신 지역에 따라 다음 웹사이트를 권장합니다:

또한 다음 목록에서 웹사이트를 선택하실 수도 있습니다.

사이트 성능 최적화 방법

최고의 사이트 성능을 위해 중국 사이트(중국어 또는 영어)를 선택하십시오. 현재 계신 지역에서는 다른 국가의 MathWorks 사이트 방문이 최적화되지 않았습니다.

미주

- América Latina (Español)

- Canada (English)

- United States (English)

유럽

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)