Generate Code That Has Multiple Test Benches

You can generate code that has multiple test benches from your subsystem. For the generated code to have multiple test benches, the input to your subsystem must consist of multiple signal groups.

To generate multiple test benches for your subsystem:

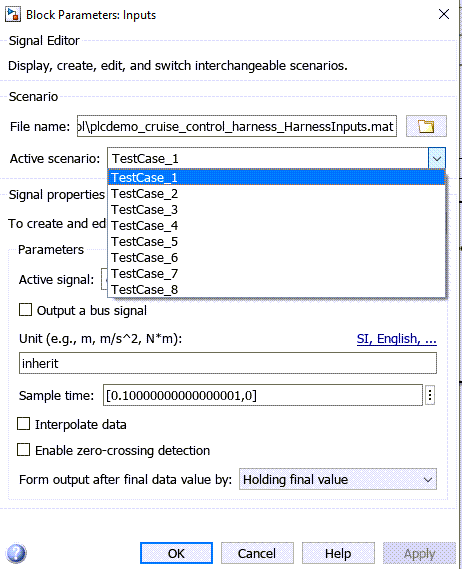

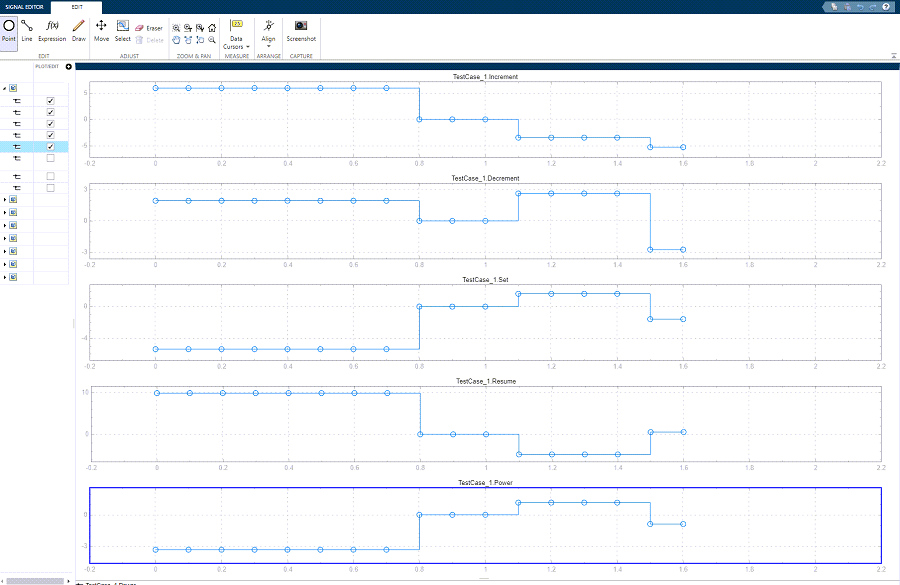

Provide multiple signal groups as inputs by using a Signal Editor block that has multiple signal groups.

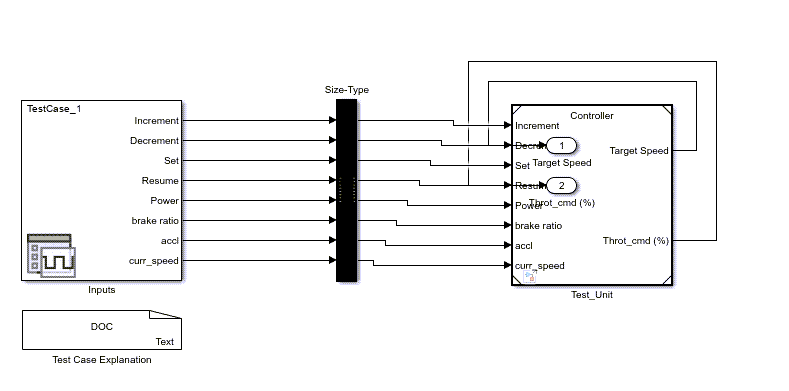

Use Simulink® Design Verifier™ to create a test harness model from the subsystem. In the test harness model, a Signal Editor block that has one or more signal groups provides input to the subsystem. Use this Signal Editor block to provide inputs to your subsystem. If your model is complex, Simulink Design Verifier can create a large number of signal groups. See Troubleshooting: Test Data Exceeds Target Data Size.

To create your Signal Editor block:

Right-click the Subsystem block. To add the Design Verifier app options to the menu, point to Select Apps and click the Design Verifier button

.

. Right-click the subsystem block and in the Design Verifier app section, select

Test Generation for Subsystemand click Generate Tests.In the Simulink Design Verifier Results Summary window, select Create harness model.

Open the Inputs block in the test harness model. The Inputs block is a Signal Editor block that can have one or more signal groups.

In the Signal Editor window, make sure that more than one signal group is available in the Active Scenario drop-down list.

Copy the Signal Editor block from the test harness mode. Use this block to provide inputs to your original subsystem.

Generate test benches for the subsystem:

Open the PLC Coder app. Click PLC Code tab > Settings > PLC Code Generation.

Select the Generate testbench for subsystem option.

Open your model and open the PLC Coder App. Click Settings, and then select Verify Code in IDE.

In your target IDE, you can see multiple test benches. Each test bench corresponds to a signal group.

Troubleshooting: Test Data Exceeds Target Data Size

If the test data from the multiple signal groups exceeds the maximum data size on your target, you can encounter compilation errors. If you encounter compilation errors when generating multiple test benches, try one of the following:

Reduce the number of signal groups in the Signal Editor block and regenerate the test benches.

Increase the simulation step size for the subsystem.

Limitations

When you are switching between signal groups, the model simulation time must remain the same for the entire simulation. Do not change the model simulation time.