Interleave

Convert separate Cb and Cr components into interleaved CbCr frame

Libraries:

SoC Blockset Support Package for AMD FPGA and SoC Devices /

MPSoC /

ZCU102

SoC Blockset Support Package for AMD FPGA and SoC Devices /

MPSoC /

ZCU106

SoC Blockset Support Package for AMD FPGA and SoC Devices /

Zynq-7000 /

PicoZed

SoC Blockset Support Package for AMD FPGA and SoC Devices /

Zynq-7000 /

ZC702

SoC Blockset Support Package for AMD FPGA and SoC Devices /

Zynq-7000 /

ZC706

SoC Blockset Support Package for AMD FPGA and SoC Devices /

Zynq-7000 /

ZedBoard

Description

Add-On Required: This feature requires the SoC Blockset Support Package for AMD FPGA and SoC Devices add-on.

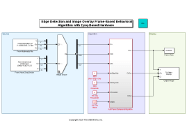

The Interleave block accepts separate Cb and Cr frame components. The output is a frame consisting of interleaved Cb and Cr data. Use this block to prepare for conversion from frames to pixel-streaming when targeting YCbCr 4:2:2 format on the FPGA with an HDMI FMC card.

Note

This block does not support HDL code generation, and you cannot use this block inside the FPGA user logic.

The FPGA data path for YCbCr 4:2:2 format consists of a Y component and a time-interleaved CbCr component. The pixel-streaming subsystem targeted for the user logic on the FPGA must have these two input and output ports. Captured YCbCr video data from board comes into Simulink® as three component frames. The horizontal size of the Cb and Cr frames is half the size of the Y component. For pixel-streaming design, recreate an interleaved CbCr component by combining the Cb and Cr frames before converting to a pixel stream. When you convert the frame to pixel streams, use dummy data (duplicate the interleaved CbCr frame) for the third component. See the Frame to Pixels for YCbCr 4:2:2 block in the YCbCr 4:2:2 HDL Pixel-Streaming Algorithm template, and the example models.

Examples

Ports

Input

Output

Version History

Introduced in R2016a