Block Reduction

Block reduction achieves faster execution during model simulation and in generated code. When block reduction is enabled, certain block groups can be collapsed into a single block, or even removed entirely.

With Simulink® Design Verifier™, block reduction happens automatically, and blocks in unused code paths are eliminated from the model. Simulink Design Verifier results do not include test objectives for blocks that have been reduced.

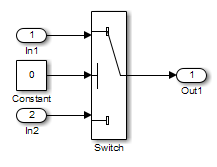

Consider the Switch block in the following model.

For this Switch block, the control input is always 0. If the

Criteria for passing first input block parameter is u2

~= 0, the Switch block always passes

the third input through to the output port. When you analyze this model, Simulink

Design Verifier removes the Switch block from the model and does not report

any test objectives for the Switch block.

For more information about block reduction, see the description of the Block reduction parameter.