이 번역 페이지는 최신 내용을 담고 있지 않습니다. 최신 내용을 영문으로 보려면 여기를 클릭하십시오.

Complex to Real-Imag

복소 입력 신호의 실수부와 허수부 출력

라이브러리:

Simulink /

Math Operations

HDL Coder /

Math Operations

설명

Complex to Real-Imag 블록은 입력 신호의 실수부 및/또는 허수부를 출력 파라미터 설정에 따라 출력합니다. 실수 출력은 복소수 입력과 동일한 데이터형입니다. 입력은 복소 신호로 구성된 배열(벡터 또는 행렬)이 될 수 있으며, 이 경우 출력 신호는 동일한 차원의 배열입니다. 실수 배열에는 대응하는 복소수 입력 요소의 실수부가 포함됩니다. 마찬가지로 허수 출력에는 입력 요소의 허수부가 포함됩니다.

예제

포트

입력

출력

파라미터

블록 특성

데이터형 |

|

직접 피드스루 |

|

다차원 신호 |

|

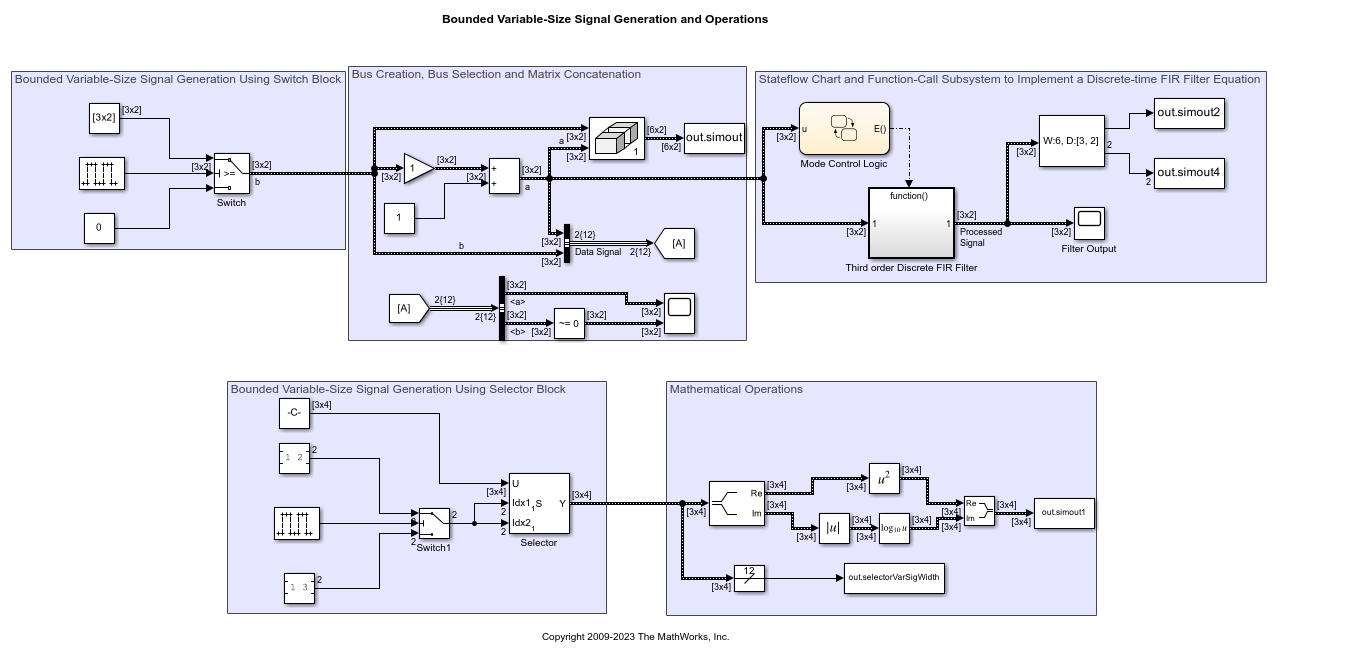

가변 크기 신호 |

|

영점교차 검출 |

|

확장 기능

버전 내역

R2006a 이전에 개발됨