Generate Structured Text Code for a Stateflow Chart That Uses Absolute-Time Temporal Logic

Model, simulate, and generate code for a Stateflow® chart that uses absolute-time temporal logic. Absolute-time temporal logic tracks elapsed time since the state became active. Absolute-time temporal logic is used in industrial applications on programmable logic controllers (PLCs) to implement logic for processes that transition between process steps by using a combination of logic-and time-based transitions. After verifying that the model functions for your requirements, generate code for the Stateflow® chart by using Simulink® PLC Coder™.

Model Description

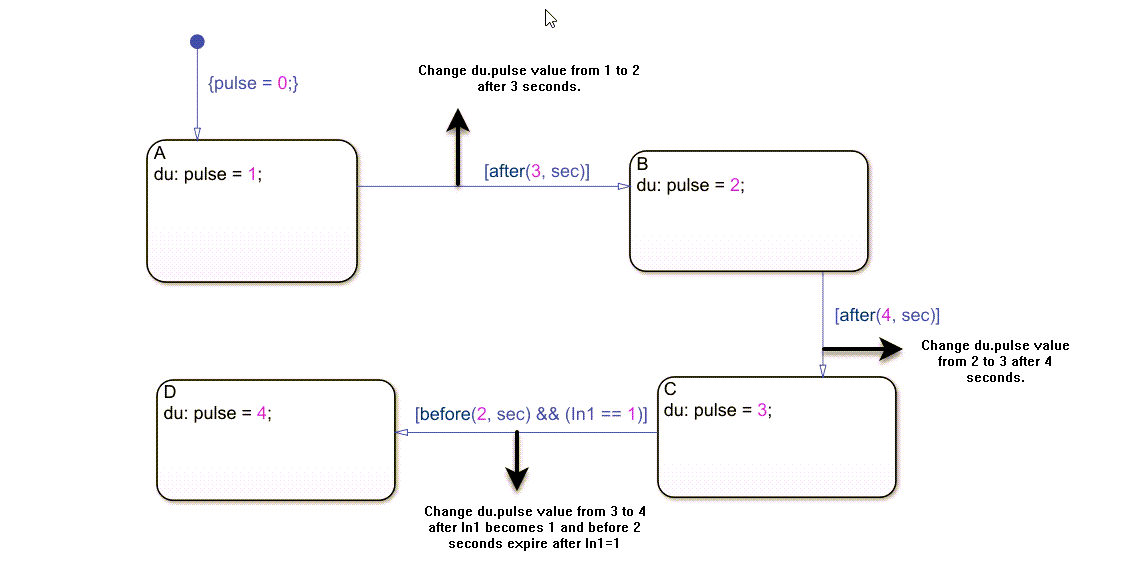

The model has a simple Stateflow® chart called Temporal. The chart transitions between four states that use absolute-time temporal logic. Verify that the transitions occur at the designed times by simulating the model and opening the Scope block. This image shows the absolute-time temporal logic based transitions inside the Temporal chart.

Open the model:

load_system('plcdemo_sf_abs_time'); open_system('plcdemo_sf_abs_time/Temporal');

Generate Code

To generate structured text code, do one of the following:

Open the PLC Coder app. Click

Settings > PLC Code Generation>Interface>Absolute-time temporal logic. SetAbsolute-time temporal logicto eitherTarget timerorTarget-independent counter. For more information on which option to set, see Absolute-Time Temporal Logic.Open the PLC Coder app. Select the

Temporalchart and clickGenerate PLC Code.Use the

plcgeneratecodefunction:

warning('OFF', 'plccoder:plccheckreport:UnsupportedType'); plcgeneratecode('plcdemo_sf_abs_time/Temporal');

### Generating PLC code for 'plcdemo_sf_abs_time/Temporal'. ### Using model settings from 'plcdemo_sf_abs_time' for PLC code generation parameters. ### Begin code generation for IDE Rockwell RSLogix 5000: AOI (rslogix5000). Creating PLC Code Generation Check Report plcdemo_sf_abs_time_report.html PLC check for 'plcdemo_sf_abs_time' complete with 0 errors, 4 warnings, and 0 messages. ### Emit PLC code to file. ### Creating PLC code generation report index.html. ### PLC code generation successful for 'plcdemo_sf_abs_time/Temporal'. ### Generated files: plcsrc/plcdemo_sf_abs_time.L5X

warning('ON', 'plccoder:plccheckreport:UnsupportedType');

Structure of Generated Code

The generated structured text code components depend on the setting of the Absolute-time temporal logic parameter. For more information, see Absolute-Time Temporal Logic.

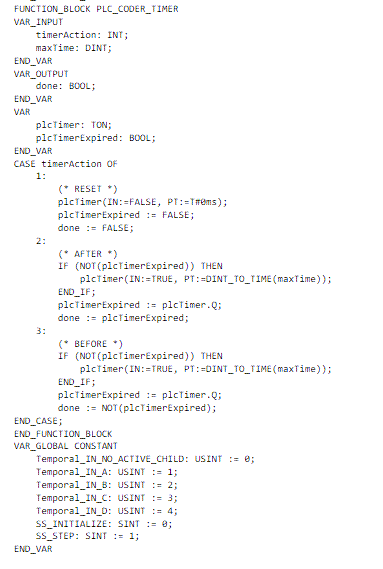

To deploy the generated code to a target PLC hardware that is supported by the target IDE, set Absolute-time temporal logic to Target timer. When you set Absolute-time temporal logic to Target timer, the generated code has a function block that implements the target integrated development environment (IDE) specific timer semantics. This image shows the function block generated for the Codesys version 2.3 target IDE.

To verify your generated code by generating a testbench, set Absolute-time temporal logic to Target-independent counter. When you set Absolute-time temporal logic to Target-independent counter the generated code implements the timer by using a target IDE independent counter block.