Implement Sqrt Block with Control Signals

This example shows how to implement the control-signal based Square root block and use it to generate HDL code.

Open and Run the Simulink Model

Specify the input data as a linear sweep. You can change these values according to your requirements.

SQRT_input = fi(1/2^17:1/2^17:1,0,18,17)';

Specify the word length for fixed-point datatypes and the latency for the model. For more information on the latency calculation, see Sqrt.

WL = 18; latency = 20;

Open the hdlcoder_sqrt_bitset_control model and specify a stop time sufficient to process all the input combinations.

stoptime = length(SQRT_input)-1+latency; open_system('hdlcoder_sqrt_bitset_control') sim('hdlcoder_sqrt_bitset_control')

This figure shows the simulation waveform for the model. You can see that dataOut output is valid when validOut is 1.

Validate Simulink Output by Using Reference Output

To validate the output of the Simulink model, compare this output to a reference values. To obtain the reference values, use the sqrt function. Compute the reference output by using the sqrt function.

ref_SQRT = sqrt(double(SQRT_input));

Use logical indexing to extract valid output.

implementation_SQRT = simulink_SQRT(valid_output);

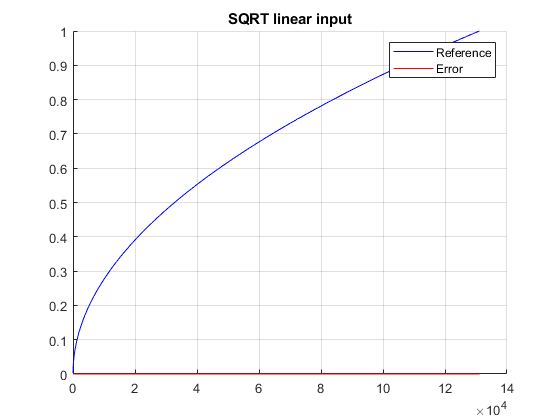

Plot the comparison results by using the comparison_plot_sqrt function. The maximum error value is significantly smaller than the output of the model.

comparison_plot_sqrt(ref_SQRT,implementation_SQRT,1,'SQRT linear input');

Maximum Error SQRT linear input 3.814697e-06 Maximum PctError SQRT linear input 3.803159e-02

Generate HDL Code for Square Root Implementation

Check the HDL settings saved of the model by using the hdlsaveparams function.

hdlsaveparams('hdlcoder_sqrt_bitset_control')

%% Set Model 'hdlcoder_sqrt_bitset_control' HDL parameters

hdlset_param('hdlcoder_sqrt_bitset_control', 'Backannotation', 'on');

hdlset_param('hdlcoder_sqrt_bitset_control', 'HDLSubsystem', 'hdlcoder_sqrt_bitset_control/Sqrt');

hdlset_param('hdlcoder_sqrt_bitset_control', 'ResetType', 'Synchronous');

hdlset_param('hdlcoder_sqrt_bitset_control', 'SynthesisTool', 'Xilinx Vivado');

hdlset_param('hdlcoder_sqrt_bitset_control', 'SynthesisToolChipFamily', 'Virtex7');

hdlset_param('hdlcoder_sqrt_bitset_control', 'SynthesisToolDeviceName', 'xc7v2000t');

hdlset_param('hdlcoder_sqrt_bitset_control', 'SynthesisToolPackageName', 'fhg1761');

hdlset_param('hdlcoder_sqrt_bitset_control', 'SynthesisToolSpeedValue', '-2');

hdlset_param('hdlcoder_sqrt_bitset_control', 'TargetDirectory', 'hdl_prj\hdlsrc');

hdlset_param('hdlcoder_sqrt_bitset_control', 'TargetFrequency', 500);

hdlset_param('hdlcoder_sqrt_bitset_control', 'Traceability', 'on');

% Set SubSystem HDL parameters

hdlset_param('hdlcoder_sqrt_bitset_control/Sqrt', 'FlattenHierarchy', 'on');

hdlset_param('hdlcoder_sqrt_bitset_control/Sqrt/LumpLatency', 'Architecture', 'MATLAB Datapath');

% Set SubSystem HDL parameters

hdlset_param('hdlcoder_sqrt_bitset_control/Sqrt/LumpLatency', 'FlattenHierarchy', 'on');

% Set Sqrt HDL parameters

hdlset_param('hdlcoder_sqrt_bitset_control/Sqrt/Sqrt', 'IterationsPerPipeline', 0);

hdlset_param('hdlcoder_sqrt_bitset_control/Sqrt/Sqrt', 'LatencyStrategy', 'Max');

hdlset_param('hdlcoder_sqrt_bitset_control/Sqrt/ValidLine', 'Architecture', 'MATLAB Datapath');

% Set SubSystem HDL parameters

hdlset_param('hdlcoder_sqrt_bitset_control/Sqrt/ValidLine', 'FlattenHierarchy', 'on');

To generate HDL code for the Sqrt block in the model, use the makehdl function.

makehdl('hdlcoder_sqrt_bitset_control/Sqrt') close_system('hdlcoder_sqrt_bitset_control') close all;

### Working on the model <a href="matlab:open_system('hdlcoder_sqrt_bitset_control')">hdlcoder_sqrt_bitset_control</a>

### Generating HDL for <a href="matlab:open_system('hdlcoder_sqrt_bitset_control/Sqrt')">hdlcoder_sqrt_bitset_control/Sqrt</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoder_sqrt_bitset_control', { 'HDL Code Generation' } )">hdlcoder_sqrt_bitset_control</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoder_sqrt_bitset_control'.

### Begin compilation of the model 'hdlcoder_sqrt_bitset_control'...

### Begin compilation of the model 'hdlcoder_sqrt_bitset_control'...

### Working on the model 'hdlcoder_sqrt_bitset_control'...

### Working on... <a href="matlab:configset.internal.open('hdlcoder_sqrt_bitset_control', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoder_sqrt_bitset_control'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdl_prj/hdlsrc/hdlcoder_sqrt_bitset_control/gm_hdlcoder_sqrt_bitset_control.slx')">hdl_prj/hdlsrc/hdlcoder_sqrt_bitset_control/gm_hdlcoder_sqrt_bitset_control.slx</a>

### Begin VHDL Code Generation for 'hdlcoder_sqrt_bitset_control'.

### Working on... <a href="matlab:configset.internal.open('hdlcoder_sqrt_bitset_control', 'Traceability')">Traceability</a>

### Working on hdlcoder_sqrt_bitset_control/Sqrt/Sqrt as hdl_prj/hdlsrc/hdlcoder_sqrt_bitset_control/Sqrt_block.vhd.

### Working on hdlcoder_sqrt_bitset_control/Sqrt as hdl_prj/hdlsrc/hdlcoder_sqrt_bitset_control/Sqrt.vhd.

### Generating package file hdl_prj/hdlsrc/hdlcoder_sqrt_bitset_control/Sqrt_pkg.vhd.

### Code Generation for 'hdlcoder_sqrt_bitset_control' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3233028_1586773/tp309ca78f/hdlcoder-ex92585700/hdl_prj/hdlsrc/hdlcoder_sqrt_bitset_control', '/tmp/Bdoc26a_3233028_1586773/tp309ca78f/hdlcoder-ex92585700/hdl_prj/hdlsrc/hdlcoder_sqrt_bitset_control/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3233028_1586773/tp309ca78f/hdlcoder-ex92585700/hdl_prj/hdlsrc/hdlcoder_sqrt_bitset_control/Sqrt_report.html

### HDL check for 'hdlcoder_sqrt_bitset_control' complete with 0 errors, 0 warnings, and 0 messages.

### HDL code generation complete.

Sqrt Block Synthesis Performance

This figure shows the Sqrt block synthesis performance on the Xilinx® Virtex® 7 and Intel® Stratix® V devices.