Generate Board-Independent HDL IP Core for Microchip Platforms

This example shows how to generate an HDL IP core for generic Microchip platform. You generate an HDL IP core for an LED blinking model, then integrate this HDL IP core into a target Microchip platform of your choice. You can generate a board-independent custom IP core to use in an embedded system integration environment, such as Microchip Libero SoC tool.

Generate Board-Independent IP Core

To generate a board-independent custom IP core for an LED blinking model, follow these steps:

1. Open the hdlcoder_led_blinking_4bit model and click the led_counter subsystem.

open_system('hdlcoder_led_blinking_4bit');

2. Set the path to the Microchip Libero SoC synthesis tool by using the hdlsetuptoolpath function:

hdlsetuptoolpath('ToolName', 'Microchip Libero SoC', 'ToolPath', liberopath);

Use your own Libero SoC installation path when executing the command. See HDL Language Support and Supported Third-Party Tools and Hardware for the latest supported version of the synthesis tool.

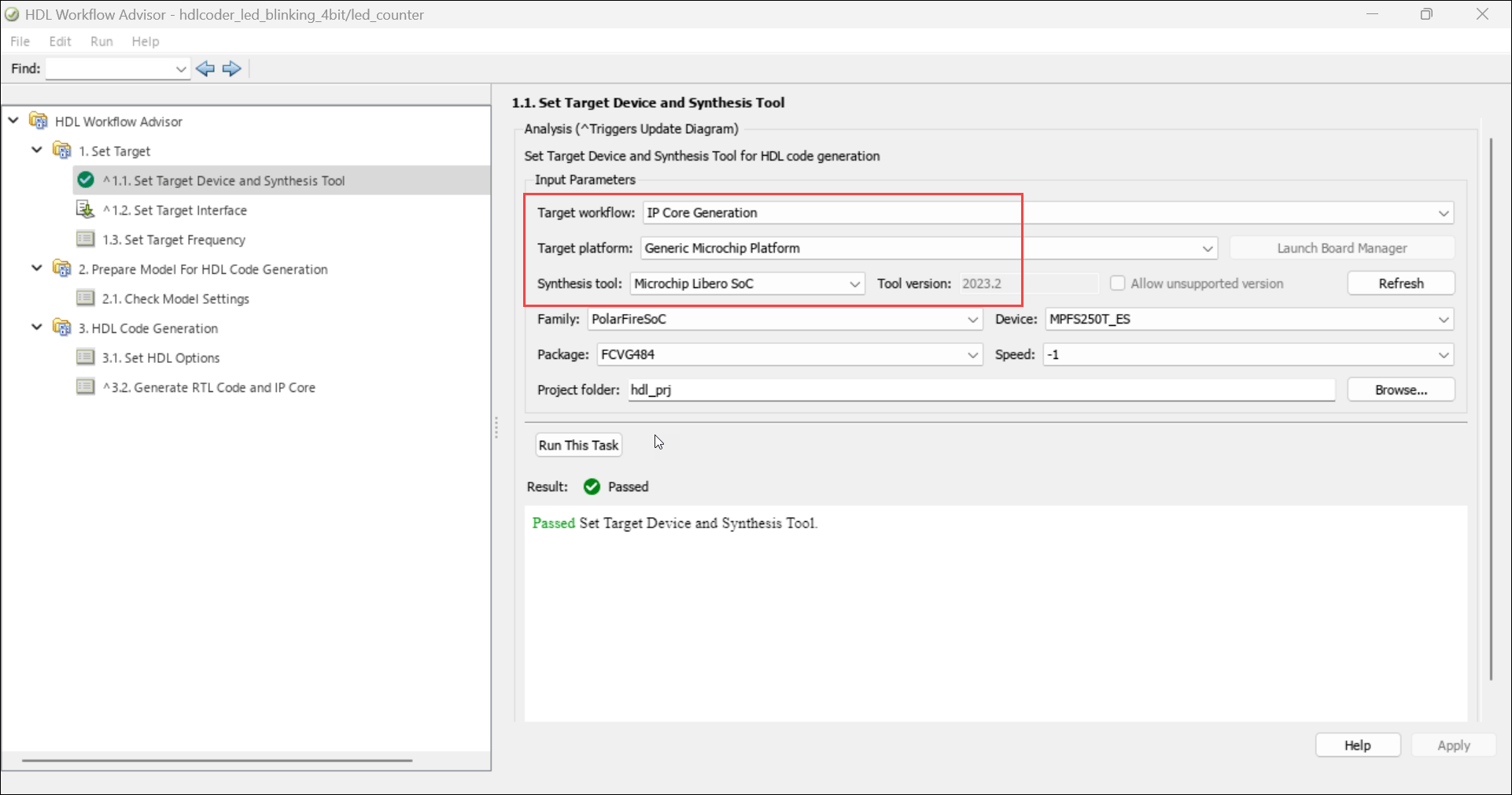

3. Open the HDL Workflow Advisor for the subsystem representing the device under test (DUT). For the LED blinking model, the led_counter subsystem represents the DUT. In the Set Target > Set Target Device and Synthesis Tool task:

Set Target workflow to

IP Core Generation.Set Target platform to

Generic Microchip Platform.Click Run This Task.

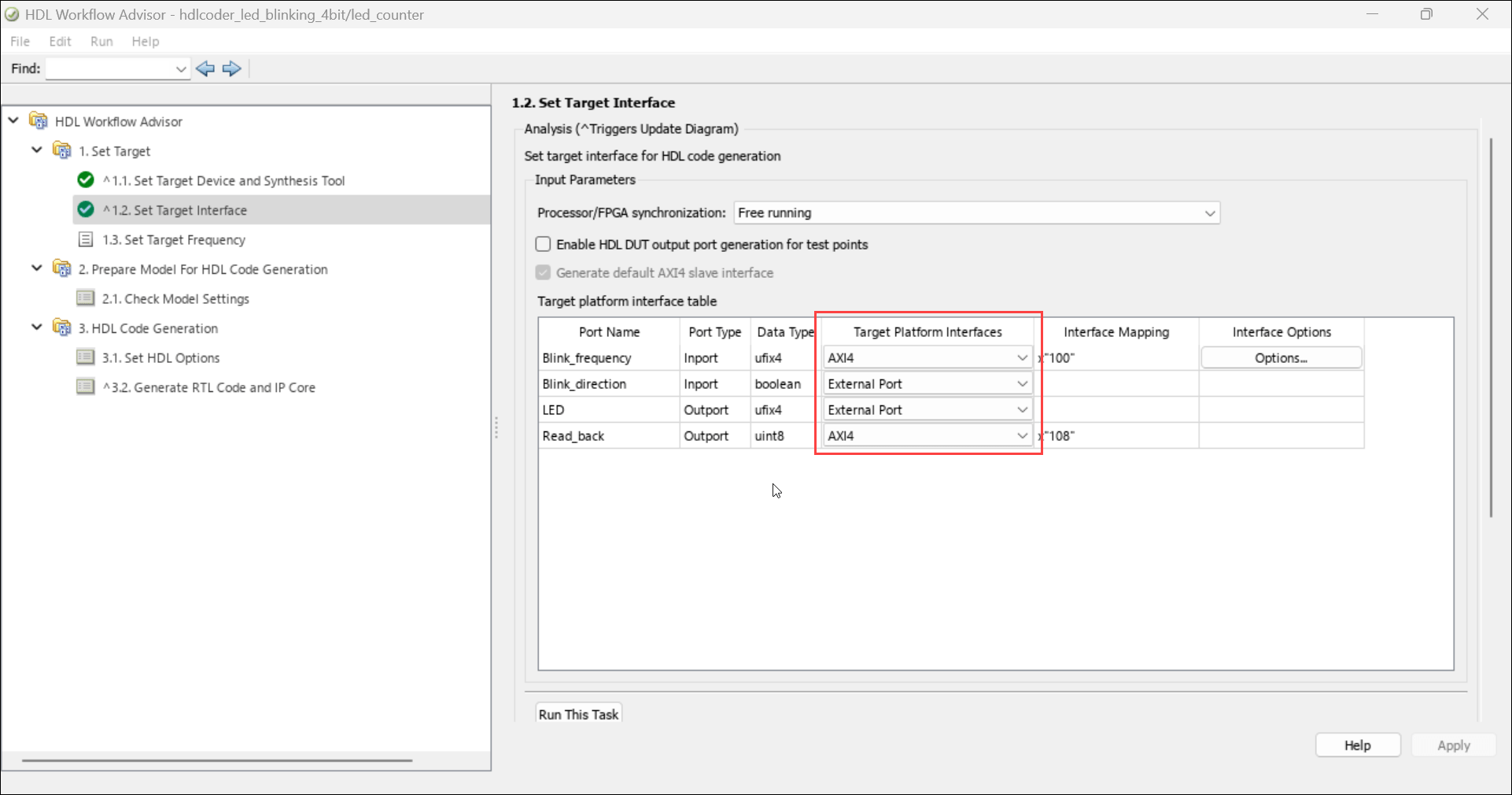

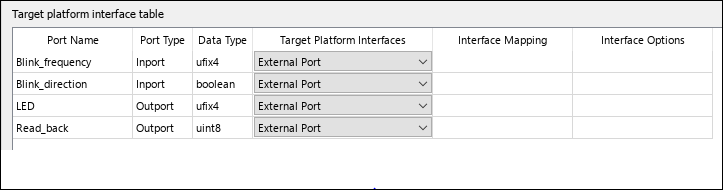

4. In the Set Target > Set Target Interface task, select a Target Platform Interface value for each port, and then click Apply. You can map each DUT port to the AXI4-Lite or AXI4 interface. For more information about these interfaces, see Target Platform Interfaces.

If you do not want to map the DUT ports to AXI4 slave interfaces, map them to external Port interfaces.

5. In the HDL Code Generation > Set HDL Options, click HDL Code Generation Settings to set HDL configuration parameters.

6. In the HDL Code Generation > Generate RTL Code and IP Core task, you can specify these options:

Option to connect the DUT IP core to multiple AXI Master interfaces. By default, the AXI4 Slave ID Width value is

12, which indicates that you can connect the HDL IP core to one AXI Master interface. To connect the DUT IP core to multiple AXI Master interfaces, to increase the AXI4 Slave ID Width parameter value. When you run this task, this setting is saved on the DUT as the HDL block property AXI4SlaveIDWidth.Option to generate the default AXI4 slave interface. By default, HDL Coder™ generates AXI4 slave interfaces for signals such as the clock, reset, ready, and timestamp. If you do not want to generate AXI4 slave interfaces, clear the Generate default AXI4 slave interface check box. Click Run This Task. When you clear the check box and run the task, the code generator saves this setting in the DUT subsystem as the HDL block property GenerateDefaultAXI4Slave.

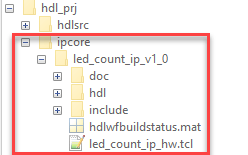

After running the task, HDL Coder generates the IP core files in the output folder in the IP core folder field, including the HTML documentation. To view the IP core report, click the link in the message window.

Insert HDL IP Core in Microchip Libero SoC SmartDesign Project

To import generated HDL IP Core into Libero SmartDesign Project, follow the below process.

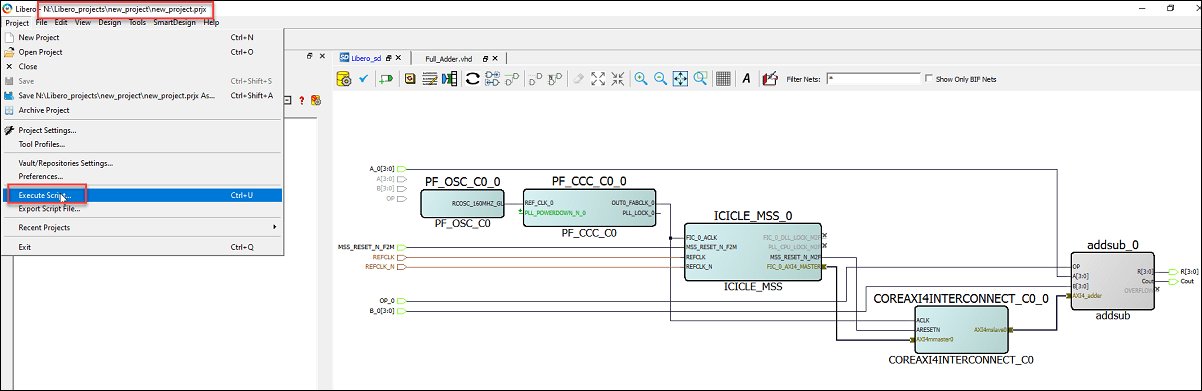

1. Open Microchip Libero Project in which HDL Coder IP needs to be imported. In the Project pane, click Execute Script.

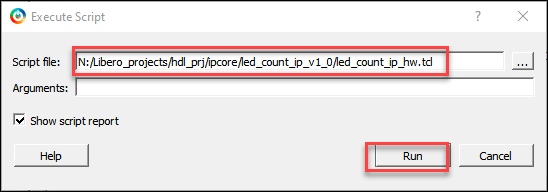

2. In Script file, choose the led_count_hw_ip.tcl file from N:/Libero_Projects/hdl_prj/ipcore/led_count_ip_v1_0 folder. Click Run.

3. After running led_count_hw_ip.tcl script, HDL Coder IP gets imported into Microchip Libero Project.

4. Instantiate HDL Coder IP by drag and drop of led_count_ip module into SmartDesign.

5. Connect led_count_ip Clock, Reset ports and Interfaces to other IP's Ports and interface as per requirement. This will form a complete Reference Design.

6. Now, You can follow next steps of implementation in Microchip Libero Tool.

Conclusion and Further Exploration

This example shows how to generate an HDL IP core using a generic microchip platform and integrate the generated IP core into Libero SmartDesign. You can integrate other IP cores into Libero SmartDesign and use these cores to create a complete reference design.