AXI4-Interface Read

Read data from IP core on AMD SoC Device

Add-On Required: This feature requires the Embedded Coder Support Package for AMD SoC Devices add-on.

Description

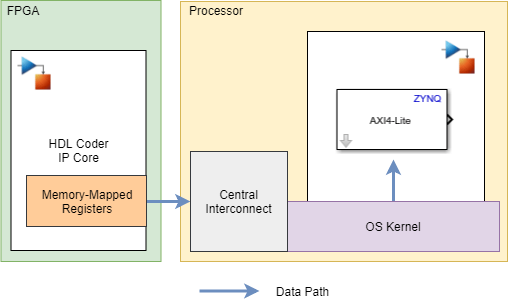

This block reads a data vector from a contiguous group of memory-mapped registers on an HDL Coder™ generated IP core. The AXI4-Interface Read block, using the central interconnect of the processing system, provides simple memory-mapped communication with the IP core on the FPGA. This block is best suited for low-throughput communication, such as inspecting status, state, or control registers.

Ports

Output

Parameters

Version History

Introduced in R2013a