Common Problems and Fixes

Hardware Mapping tool not reflecting latest model configuration

Problem

When the Hardware Mapping tool is open and add or delete the peripheral blocks in the model, the Hardware Mapping tool does not reflect the changes.

Possible Solution

Close the existing Hardware Mapping tool and re-open the Hardware Mapping tool. The updated changes should now be visible in the Hardware Mapping tool.

Pin information on the block is not updated

Problem

In the Hardware Mapping tool, when you configure the pin for the peripheral block and the respective block mask in the model does not reflect the changes.

Possible Solution

Go to the model and press Ctrl+D or click Update Model under Modeling tab to view the changes made in the model.

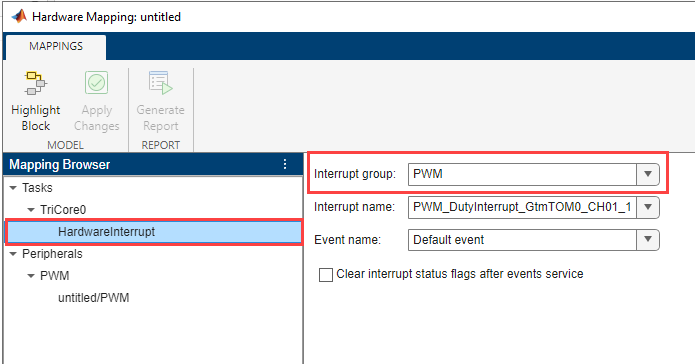

Model build failures when trace variables enabled in virtualizer studio (VDK)

Problem

When the variables are selected for tracing in the virtualizer studio (VDK) and you encounter the following build error while building the Simulink model.

Possible Solution

The elf is locked by the VDK and deleting it is not possible. You can try any one of the following solutions:

Try to generate the code in different folder.

Rename the model.

Close and relaunch the VDK.

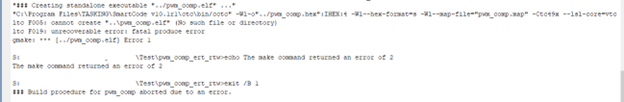

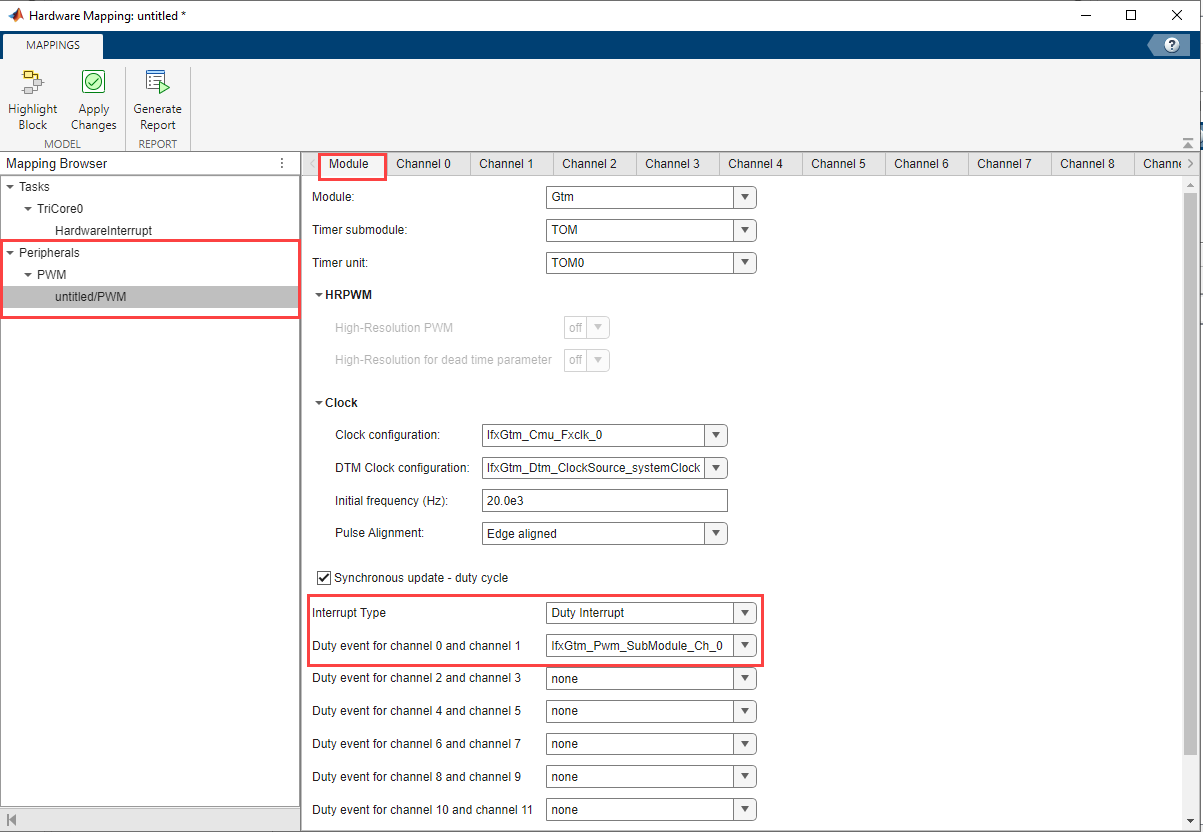

PWM interrupts do not reflect in Task Map

Problem

When you try to configure the PWM peripheral and perform the following:

Set the Interrupt type to

Duty Interrupt.Select the Duty event for channel #

Now try to map the task for Interrupt group. The PWM Interrupts does not reflect in the Interrupt Group.

Possible Solution

Try to click on the respective Channel tab for the selected

Duty event for channel # and then try to configure the task map for

the Interrupt Group. Now you should be able to view the PWM interrupts available in the

Interrupt Group.

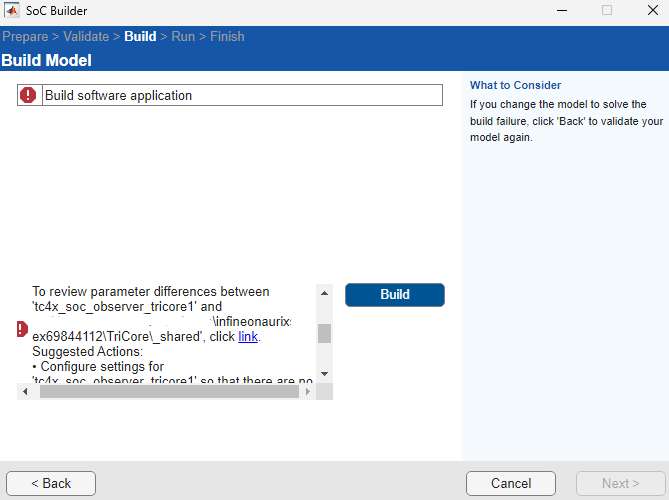

Build errors while using SoC Builder tool

Problem

When you try to build a top-level model with referenced models, SoC Builder tool throws the build error for parameter differences in the referenced models.

Possible Solution

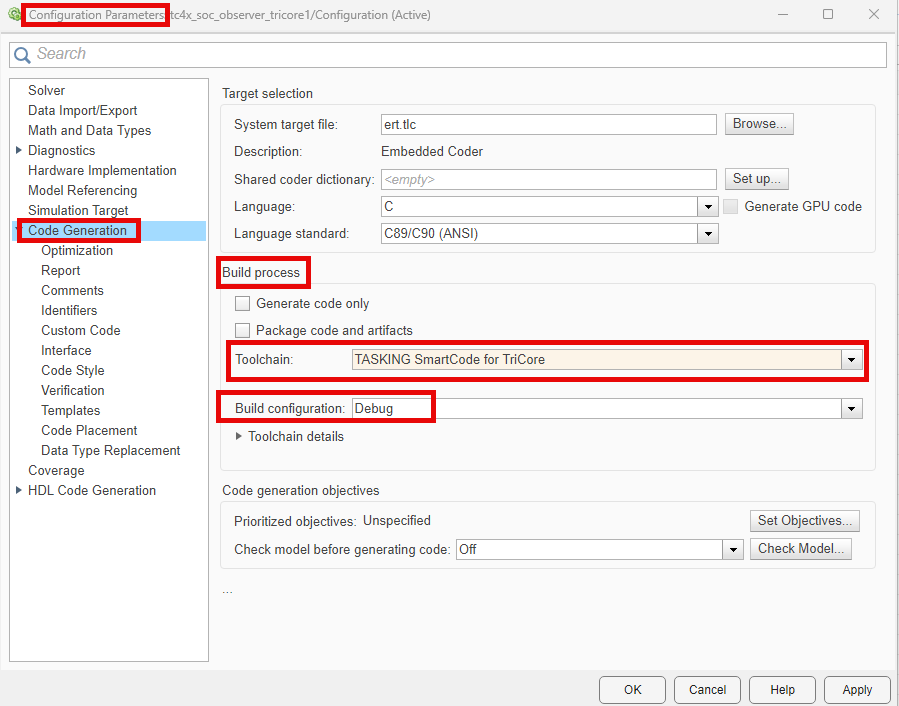

The Toolchain and Build configuration parameters must match for all referenced models in a top-level model. You can change this parameter by navigating to Code generation > Build process > Toolchain (Build configuration) in Configuration Parameters window of the referenced models.

Linker errors while using SoC Builder tool

Problem

When you try to build a top-level model with referenced models and generate a single executable file for all participating homogenous TriCore processing units using SoC Builder tool, you can encounter the linker errors in the MATLAB® Command Window.

![]()

Possible Solution

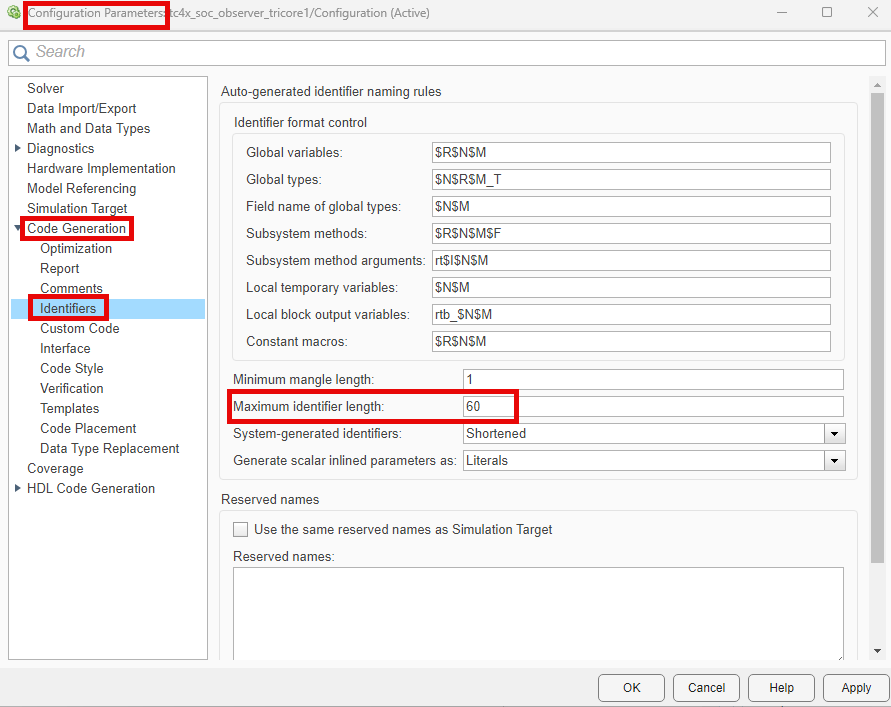

Simulink® truncates the variable names if the maximum identifier length for the models is insufficient. This truncation results in duplicate variables and software interface model names, which can cause linker errors.

You can change the identifier length for a particular referenced model by navigating to Code Generation > Identifiers > Maximum identifier length in the Configuration Parameter window. For more information, see Insufficient maximum identifier length.

You must ensure that the global variables and data storage variables are different in different referenced models of the top-level model to avoid linker errors. If you encounter linker error due to similar variable names, change their name or use Interprocess Data Read, Interprocess Data Write, and Interprocess Data Channel blocks for sharing the global variables between the referenced models.

SIL/PIL Signal logging warning

Problem

During SIL/PIL simulation while logging directly the inports or outports of driver blocks throws a following warning:

Warning

mTopModelPIL_with_Peripherals/Sumdiff_Subsystem/TMADC, 'Output Port 1': Signal not found in code description, or signal is virtual, inactive, or has a variable size.

Possible Solution

User cannot log driver blocks during SIL/PIL and logging of input ports or output ports is not supported.

Issue saving Simulink models to previous MATLAB version

When you try to save a Simulink model of R2023a or later version to earlier MATLAB version, you will encounter an error message. This is due to the unification SoC and EC boards, their features are merged from R2023a. We cannot back port to a particular HSP (EC or SoC) compatible models for R2023a and later.

Exported Simulink models are not working

Embedded Coder® Support Package for Infineon® AURIX™ TC4x Microcontrollers does not support backward compatibility for the Simulink models. Simulink models based on Infineon AURIX microcontrollers exported to earlier versions of Simulink will not work as expected.

For example, if you export a model from R2024b to earlier versions like R2024a, R2023b, or R2023a, these models do not work. However, you can use the models from earlier versions in later versions of Simulink, as forward compatibility is supported.

Run time issues during code generation

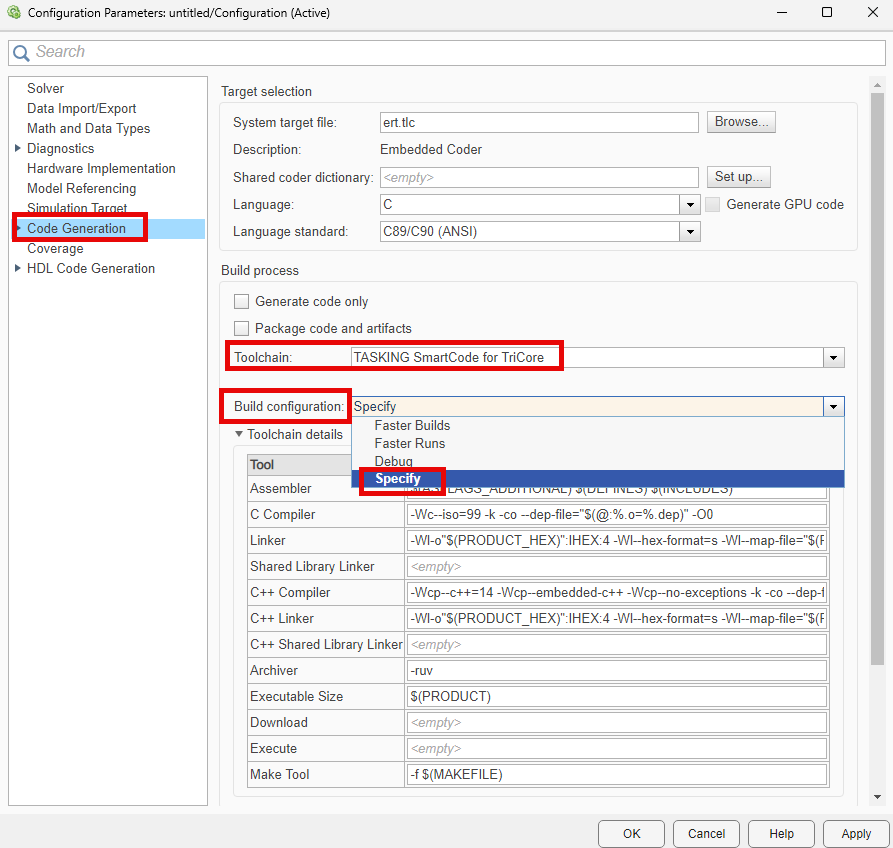

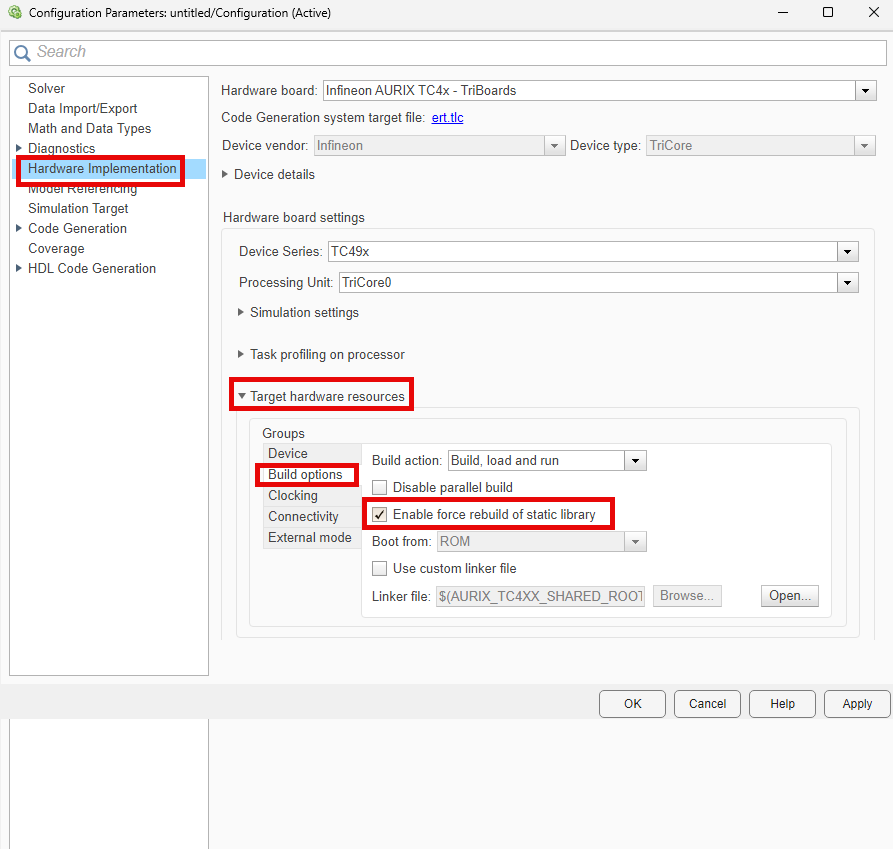

If you change the Toolchain parameter and set Build

configuration parameter to Specify in the

Configuration Parameters window, you must select Enable force rebuild of static

library to rebuild iLLD and avoid run time issues during the code

generation.

However, if you modify the Toolchain parameter and then set the

Build configuration parameter to Faster

Builds, Faster Runs, or

Debug, Simulink automatically rebuilds iLLD. You no longer need to enable the Enable

force rebuild of static library parameter

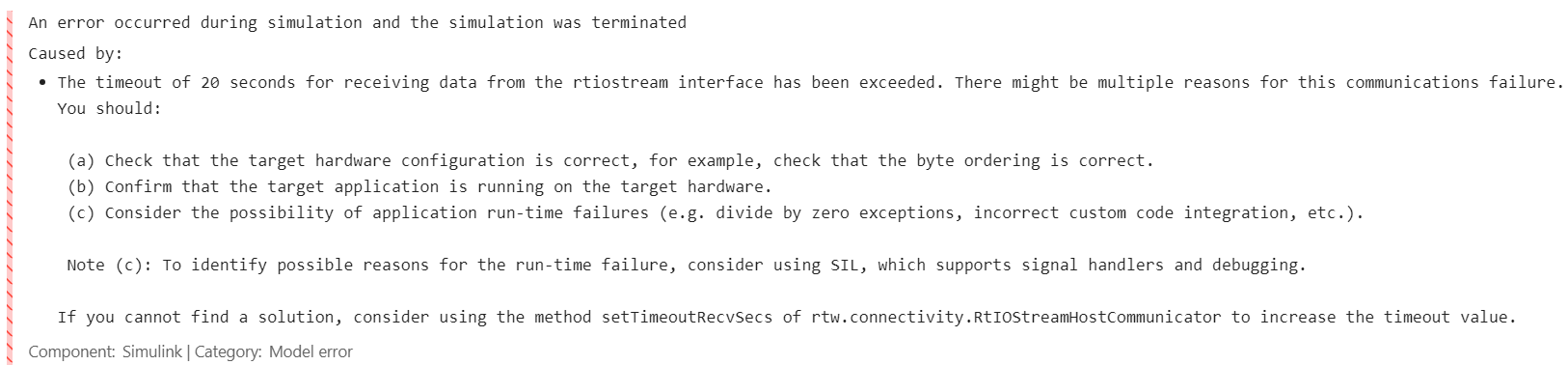

PIL timeout issues in models using parallel processing unit (PPU) core

Problem

When you try PIL simulation on models with PPU core of Infineon TC4x hardware boards, Simulink throws this CRL PIL time out error in the Diagnostic Viewer.

Possible Solution

Analyze the partial PIL results to identify the possible cause of the error. You can also try these solutions.

Use higher optimization with lower granularity of PIL profiling to reduce stack size usage.

Use a custom linker file to set stack sizes appropriately.

Connectivity issues after disconnect during external mode simulation

Problem

If you disconnect a Simulink model with peripheral interrupts during Monitor & Tune or external mode, simulation does not reconnect and stays in the initialization state.

Possible Solution

Build the model, save it, and restart the external mode simulation.