# MATLAB EXPO

#### 인증 표준을 만족하기 위한 요구사항 기반 검증의 자동화 방안 류성연, MathWorks Korea

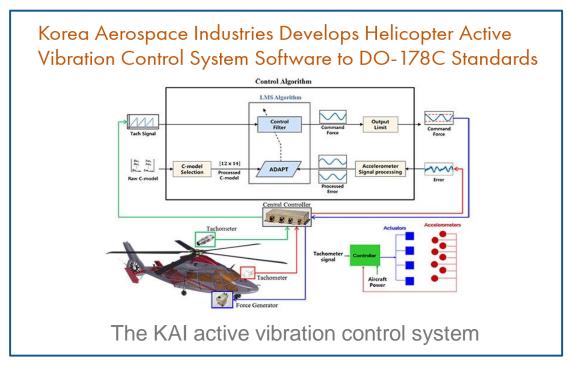

## **Challenge to Deliver Complex Systems and Meet Standards**

- Need to meet industry or customer's standards

- DO-178C (Aero), ISO 26262 (Auto), IEC 62304 (Medical), IEC 61508 (Industrial), MISRA, etc.

- Time and cost for safety critical projects estimated 20-30 times more costly\*

- Finding defects late increases cost and time

\*Source: Certification Requirements for Safety-Critical Software

## ISO 26262-6:2018 notes Simulink and Stateflow

Table 5

|           | Notationa                                                                                                                                                                   |    | ASIL     |          |          |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----------|----------|----------|--|--|

| Notations |                                                                                                                                                                             | Α  | В        | C        | D        |  |  |

| 1a        | Natural language <sup>a</sup>                                                                                                                                               | ++ | ++       | ++       | ++       |  |  |

| 1b        | Informal notations                                                                                                                                                          | ++ | ++       | +        | +        |  |  |

| 1c        | Semi-formal notations <sup>b</sup>                                                                                                                                          | +  | +        | ++       | ++       |  |  |

| 1d        | Formal notations                                                                                                                                                            | +  | +        | +        | +        |  |  |

|           | Natural language can complement the use of notations for example where some topics ral language or provide an explanation and rationale for decisions captured in the notat |    | re readi | ly expre | essed in |  |  |

|           | EXAMPLE To avoid possible ambiguity of natural language when designing complex elements, a combination of an activity<br>diagram with natural language can be used.         |    |          |          |          |  |  |

| b         | Semi-formal notations can include pseudocode or modelling with UML®, SysML®, Simulink® or Stateflow®.                                                                       |    |          |          |          |  |  |

Notations for coftware unit design

UML®, SysML®, Simulink® and Stateflow® are examples of suitable products available commercially. This NOTE information is given for the convenience of users of this document and does not constitute an endorsement by ISO of these products.

NOTE In the case of model-based development with automatic code generation, the methods for representing the software unit design are applied to the model which serves as the basis for the code generation.

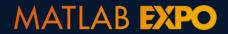

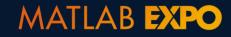

## **Qualify tools with IEC Certification Kit and DO Qualification Kit**

- Qualify code generation and verification products

- Includes documentation, test cases and procedures

## **Qualify tools with IEC Certification Kit and DO Qualification Kit**

- Qualify code generation and verification products

- Includes documentation, test cases and procedures

## **Qualify tools with IEC Certification Kit and DO Qualification Kit**

- Qualify code generation and verification products

- Includes documentation, test cases and procedures

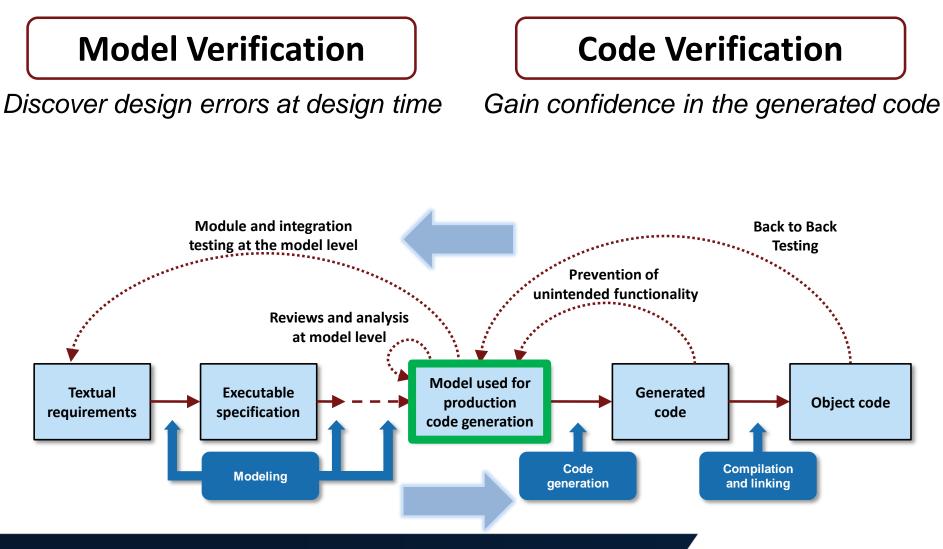

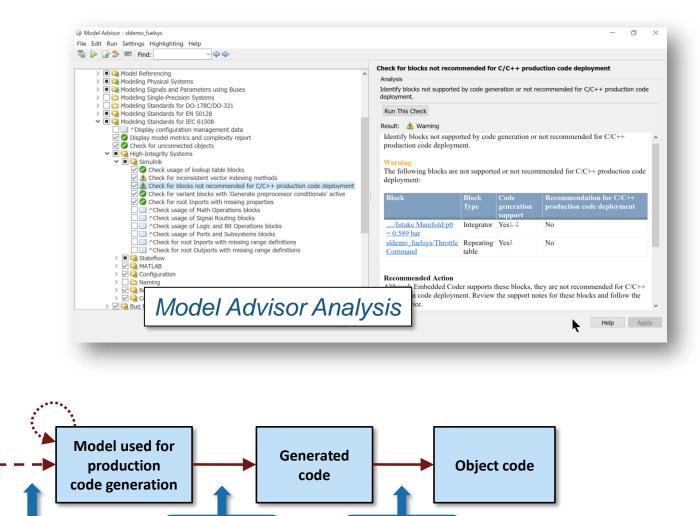

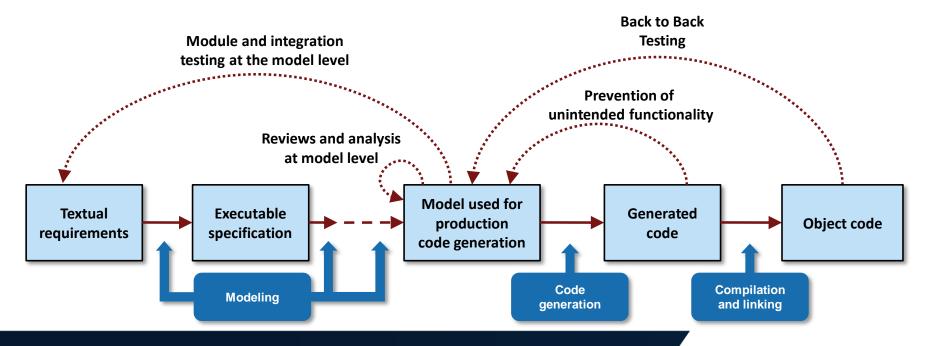

## **Conform to Certification Standards with Reference Workflow**

7

## **Model Verification: Discover Design Errors at Design Time**

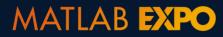

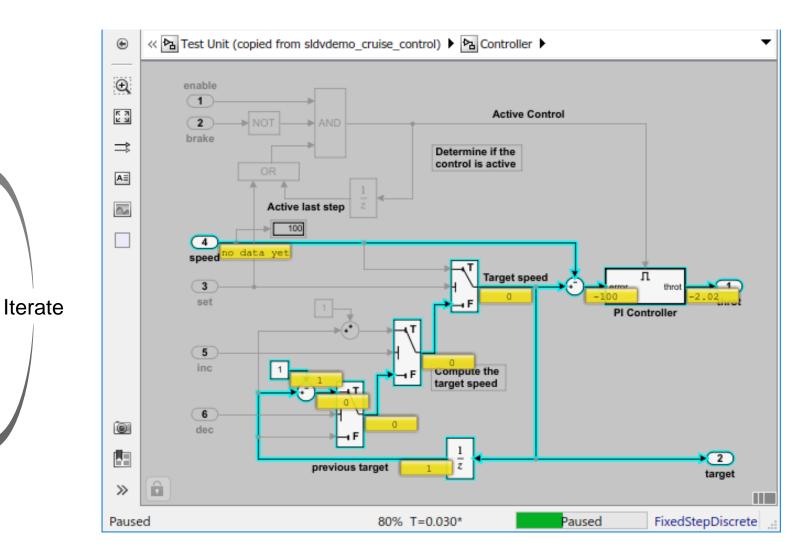

## **Code Verification: Gain Confidence in the Generated Code**

## **Manage Requirements**

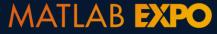

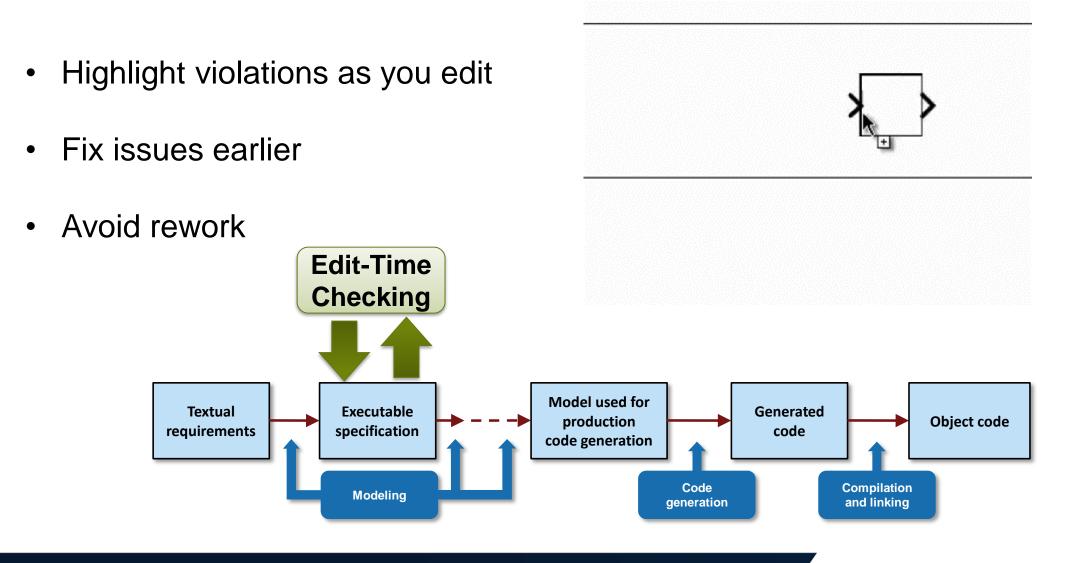

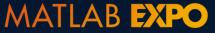

#### **Model Verification**

- Manage requirements

- Check standard compliance

- Systematically test

- Measure model coverage

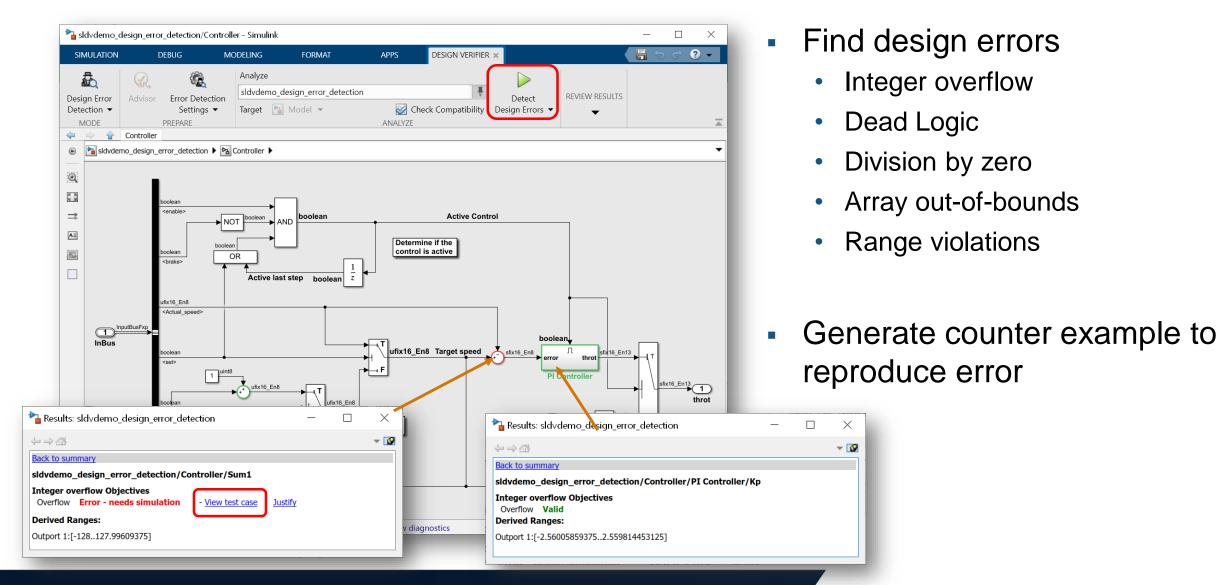

- Detect design errors

- Prove model behavior compliance

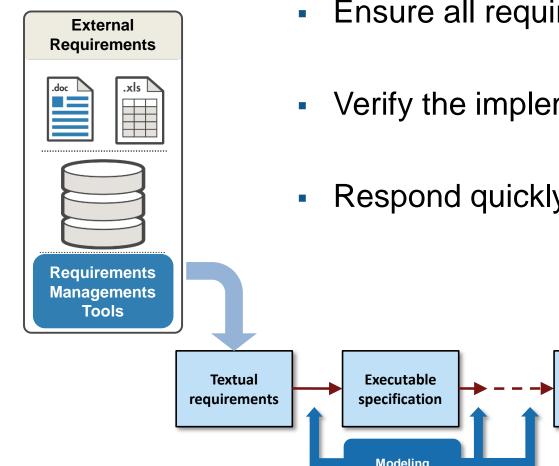

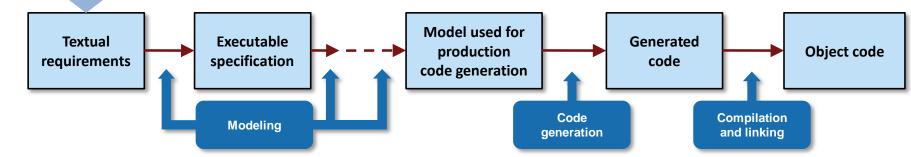

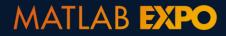

## **Manage Requirements**

- Ensure all requirements implemented

- Verify the implementation is correct

- Respond quickly to requirement changes

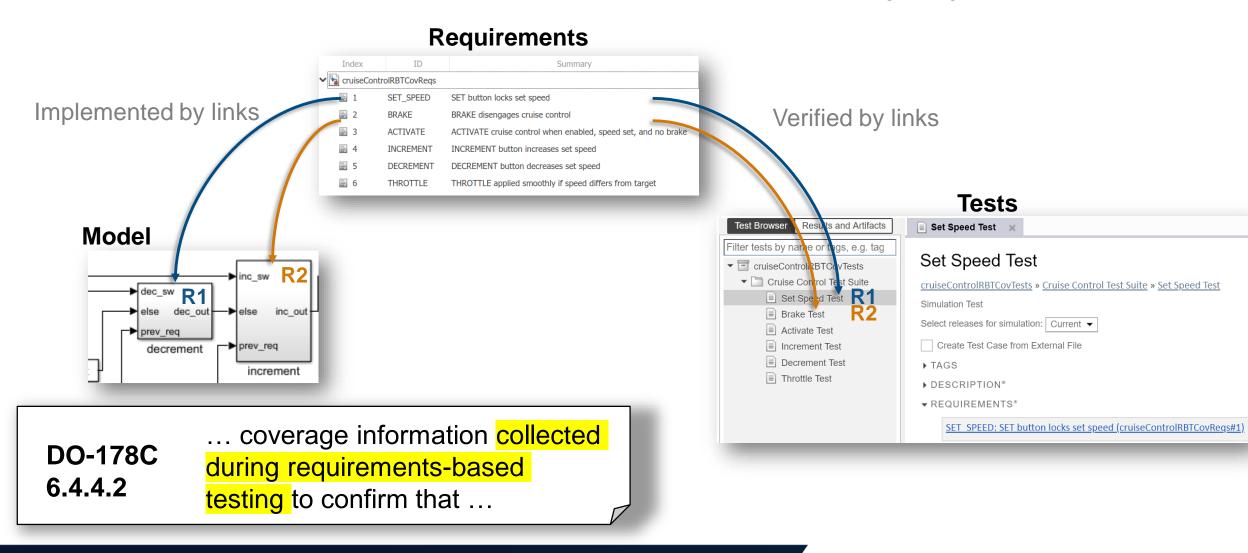

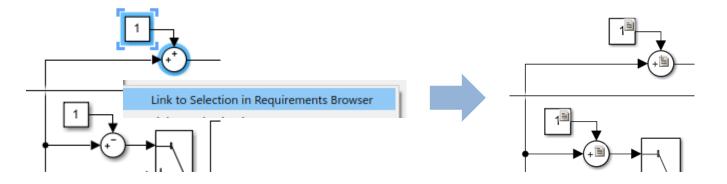

## Work with Requirements, Architecture and Design Together

## **Demo: Requirements Perspective**

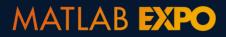

## **Test and Requirements Traceability**

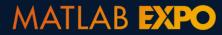

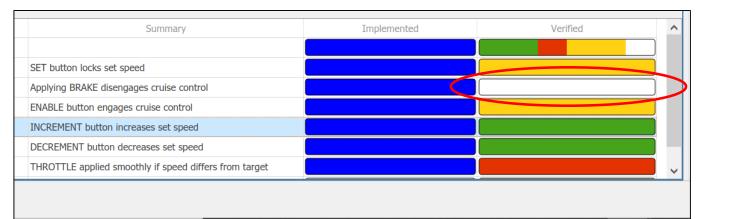

## **Review and Analyze Traceability with Traceability Matrix**

Requirement is missing link to Test Case

## Review and Analyze Traceability with Traceability Matrix

- Review links between different requirements, model, test

- Filter view to manage large sets of artifacts

- Highlight missing links

- Directly add links to address gaps

## **Systematic Functional Testing of Model**

#### **Model Verification**

- Manage requirements

- Check standard compliance

- Systematically test

- Measure model coverage

- Detect design errors

- Prove model behavior compliance

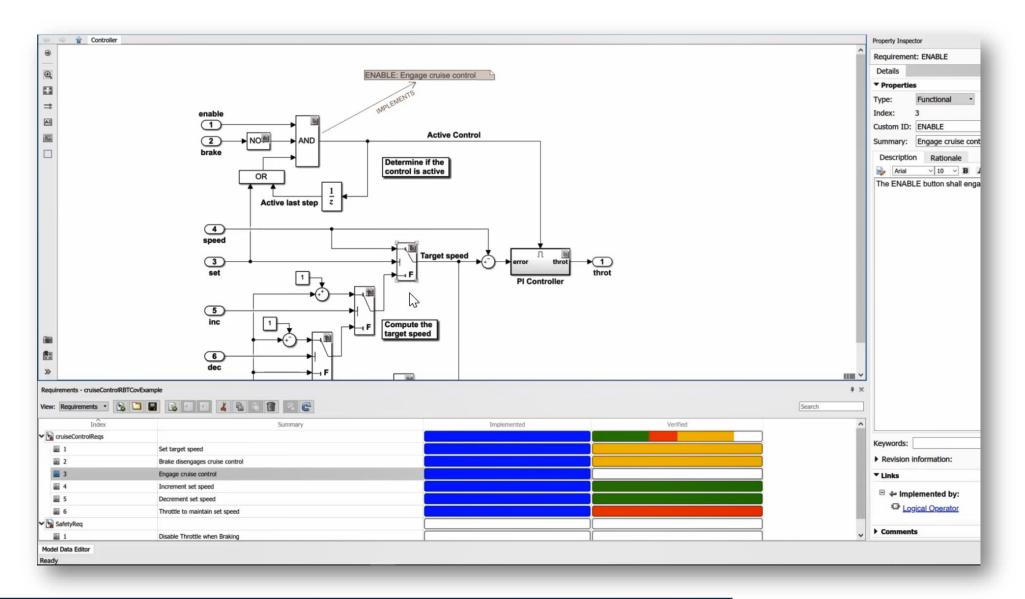

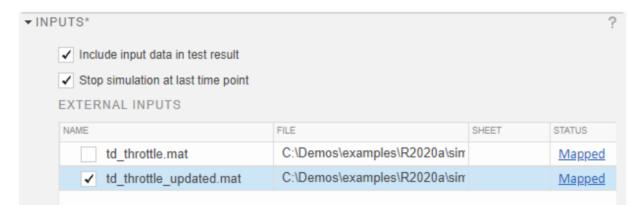

## **Overview to Requirements-Based Test**

Goal: Assess extent to which requirements-based tests exercise corresponding designs

## **Requirements Based Verification with Simulink Test**

## Automate Functional Testing with Simulink Test

#### **Test Manager**

- ✓ Create test cases

- Group into suites and test files

- Execute individual or batch

- ✓ View result summary

- ✓ Analyze results

- ✓ Archive, export, report

MATLAB **EXPO**

|                                                            |                            |                                                                          |                               |                                  | Include in Report         Image: Test Details       Iterations         Logged Signals       External Inputs         Callback Scripts       Parameter Overrides         Coverage Settings       Logical and Temporal Assessments         System Under Test       Baseline Criteria         Custom Criteria       Equivalence Criteria         Test File Options       Configuration Settings |                                   |                 |              |                                       |                                   |                                                                     |

|------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------|-------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------|--------------|---------------------------------------|-----------------------------------|---------------------------------------------------------------------|

| FILE                                                       | EDIT BU                    | RESULTS RESOURCES                                                        |                               |                                  | Output Option                                                                                                                                                                                                                                                                                                                                                                               |                                   |                 |              |                                       |                                   |                                                                     |

|                                                            | Results and Artifacts      | M Start Page × Slow Accel ×                                              |                               |                                  | File Format:                                                                                                                                                                                                                                                                                                                                                                                | PDF                               | -               |              | ort_5.pdf - Adobe Re<br>View Window H |                                   |                                                                     |

| C Filter Tests                                             |                            | Slow Accel                                                               |                               |                                  | File Name:                                                                                                                                                                                                                                                                                                                                                                                  | C:\Users\D                        | esktop\ne       |              |                                       | 1 / 6 = 71.4% •                   | 💒 🔹 Sign Commen                                                     |

| General Performa                                           | ance Test                  | ComponentTesting > Functional and Regression tests > Signal Builder Base | line examples > Slow Accel    |                                  |                                                                                                                                                                                                                                                                                                                                                                                             |                                   |                 |              |                                       |                                   | E Sign Commen                                                       |

| <ul> <li>Functional and R</li> </ul>                       |                            | Baseline Test                                                            | Stow Account                  |                                  | Customization                                                                                                                                                                                                                                                                                                                                                                               | Templates                         |                 |              |                                       |                                   |                                                                     |

| 🖌 🛅 Signal Builder                                         |                            | DESCRIPTION                                                              |                               |                                  | Test Suite Re                                                                                                                                                                                                                                                                                                                                                                               | nortor Color                      | t TootSuite     | <u>e</u>     | P                                     |                                   |                                                                     |

| E Slow Acce                                                | el                         | ► REQUIREMENTS                                                           | 📣 Test Manager                | a second real of                 | Test Suite Re                                                                                                                                                                                                                                                                                                                                                                               | porter Selec                      | i Testouite     |              | Report G                              | ienerated by Test M               | anager                                                              |

| E Fast Accel                                               |                            | SYSTEM UNDER TEST                                                        | TESTS VISUAI                  | LIZE FORMAT                      | Test Case Re                                                                                                                                                                                                                                                                                                                                                                                | porter Select                     | t TestCase      |              | Title:                                | LandingGearControl-Re             | pression Tests                                                      |

| E Decel                                                    |                            | PARAMETER OVERRIDES                                                      |                               |                                  |                                                                                                                                                                                                                                                                                                                                                                                             |                                   |                 |              | Author:                               | Jessica Johnson                   |                                                                     |

| ExcelDrivenEx                                              |                            | ▶ CALL BACKS                                                             | 📃 📴 😥 🔍                       | 25 🚽 🔯                           |                                                                                                                                                                                                                                                                                                                                                                                             |                                   |                 |              | Date:                                 | 20-Feb-2015 18:28:22              |                                                                     |

| Software-in-the-lo                                         | oop Testing                | ► INPUTS                                                                 | Clear Plot 🔍 🕄 🕞 Data         | a Cursors Highlight Send to Figu | 27                                                                                                                                                                                                                                                                                                                                                                                          |                                   |                 |              | Test Environ                          | ment                              |                                                                     |

| <ul> <li>SystemTesting</li> <li>ExampleBaseline</li> </ul> | oTecting                   | ► OUTPUTS                                                                | EDIT ZOOM & PAN MI            |                                  |                                                                                                                                                                                                                                                                                                                                                                                             |                                   |                 |              | Platform:<br>MATLAB:                  | PCWIN64<br>(R2015a)               |                                                                     |

| Campiebaseine                                              | eresung                    |                                                                          |                               | Results and Artifacts            | 🖍 Start Page >                                                                                                                                                                                                                                                                                                                                                                              | <  Slow Acco                      | a x 🖂           |              |                                       |                                   |                                                                     |

|                                                            |                            | ➤ CONFIGURATION SETTINGS OVERRIDES                                       |                               |                                  | Jan Start age /                                                                                                                                                                                                                                                                                                                                                                             |                                   | E3              |              |                                       |                                   |                                                                     |

|                                                            |                            | ▼ BASELINE CRITERIA                                                      | Q Filter Results              | STATUS                           | C Activate_Pump                                                                                                                                                                                                                                                                                                                                                                             |                                   |                 |              |                                       |                                   |                                                                     |

|                                                            |                            | SIGNAL NAME ABS TOL                                                      | A Results : 2015-Jan-12       |                                  | ASSESSMENT                                                                                                                                                                                                                                                                                                                                                                                  |                                   |                 |              |                                       |                                   | SYMBOLS                                                             |

|                                                            |                            | SlowAcelbaselineCheckpoint1.mat                                          |                               |                                  | At any point of time                                                                                                                                                                                                                                                                                                                                                                        | if abs(roomTemper                 | rature - setTen | perature) >= | threshold becom                       | es true and stays true for at lea | + troomTemper                                                       |

|                                                            |                            |                                                                          | · ·                           | aseline examples 2 🥑 1 😒         | seconds then, starting                                                                                                                                                                                                                                                                                                                                                                      |                                   |                 |              |                                       | pCmd must stay true for at leas   |                                                                     |

|                                                            |                            |                                                                          | ► Slow Accel                  | 0                                | seconds                                                                                                                                                                                                                                                                                                                                                                                     |                                   |                 |              |                                       |                                   | • • • • • • • • • • • • • • • • • • • •                             |

|                                                            |                            |                                                                          | A 🖹 Fast Accel                | 8                                |                                                                                                                                                                                                                                                                                                                                                                                             |                                   |                 |              | 24                                    | Error 1 of 2                      | <del>9</del>                                                        |

|                                                            |                            |                                                                          | 🖌 📓 Baseline Cr               | riteria Result 🛛 😆               | Expected Behavio                                                                                                                                                                                                                                                                                                                                                                            | r                                 |                 | Actua        | al Result                             |                                   | Explanation                                                         |

| PROPERTY                                                   | VALUE<br>Slow Accel        |                                                                          | i gear                        | — o                              | THESER                                                                                                                                                                                                                                                                                                                                                                                      |                                   |                 | TROOP        | -                                     |                                   | Assessment 'Activate_F                                              |

| Туре                                                       | Baseline Test              |                                                                          | <ul> <li>throttle</li> </ul>  | <u> </u>                         | Notes 10                                                                                                                                                                                                                                                                                                                                                                                    | र्धक स्वत्र स्व                   | 0 150           |              | 10 12s                                | 140 140 táo                       | <ul> <li>Trigger condition<br/>(threshold)' is true at</li> </ul>   |

| Location                                                   | C:\Users\moneil\Deskto     |                                                                          | <ul> <li>vehicle s</li> </ul> | speed 🗕 🛛                        | At rising edge                                                                                                                                                                                                                                                                                                                                                                              |                                   |                 | Acris        | ing adapa                             |                                   | <ul> <li>Expected response</li> <li>i.e. with a delay of</li> </ul> |

| Enabled                                                    | ✓                          |                                                                          | ► 🖂 Sim Output                | (sf_car : normal)                | After at most the RESPONSE                                                                                                                                                                                                                                                                                                                                                                  |                                   |                 | Alter        | RESPONSE                              |                                   | <ul> <li>Expected 'pumpCm</li> </ul>                                |

| Hierarchy                                                  | ComponentTesting > Fu      |                                                                          | ► E Decel                     | ٥                                | tata -                                                                                                                                                                                                                                                                                                                                                                                      | 1 125 142                         | 14.5 180        |              | talan 120                             | 128 140 148 150                   | s is false.                                                         |

| Model<br>Simulation Mode                                   | sf_car<br>[Model Settings] |                                                                          |                               |                                  |                                                                                                                                                                                                                                                                                                                                                                                             | 21                                |                 |              | -                                     | -11                               |                                                                     |

| Harness Name                                               | SigBdriven                 |                                                                          |                               |                                  |                                                                                                                                                                                                                                                                                                                                                                                             |                                   |                 |              |                                       |                                   |                                                                     |

|                                                            |                            |                                                                          |                               |                                  | III III   Q O                                                                                                                                                                                                                                                                                                                                                                               | 9 9 5                             | h               |              |                                       |                                   |                                                                     |

|                                                            |                            |                                                                          |                               |                                  | EXPRESSION TREE                                                                                                                                                                                                                                                                                                                                                                             | PLOTS                             |                 |              |                                       |                                   |                                                                     |

|                                                            |                            |                                                                          | PROPERTY                      | VALUE                            | <ul> <li>Activate_Pump: At a<br/>time, if (abs((roomT</li> </ul>                                                                                                                                                                                                                                                                                                                            | emperature -                      | al l            | T I          |                                       |                                   |                                                                     |

|                                                            |                            |                                                                          | Name                          | i gear                           | setTemperature)) >= th<br>becomes true and stay                                                                                                                                                                                                                                                                                                                                             | reshold)<br>is true for at Untest |                 | -            |                                       |                                   |                                                                     |

|                                                            |                            |                                                                          | Status                        | 0                                | least 2 seconds then, a<br>rising edge of trigger, w                                                                                                                                                                                                                                                                                                                                        | with a delay of                   | 0 5             | 10 15        | 20 25                                 | 30 35 40 45                       | 50 55 60 65                                                         |

|                                                            |                            |                                                                          | Absolute Tolerance            | 0                                | at most 2 seconds, put<br>stay true for at least 2                                                                                                                                                                                                                                                                                                                                          | mpCmd must                        |                 |              |                                       |                                   |                                                                     |

|                                                            |                            |                                                                          | Relative Tolerance            | 0.00 %                           | <ul> <li>if (abs((roomTemp<br/>setTemperature))</li> </ul>                                                                                                                                                                                                                                                                                                                                  | perature - Tr                     | ue              | 1.1          |                                       |                                   |                                                                     |

|                                                            |                            |                                                                          | Block Path                    | SigBdriven/shift_logic           | becomes true and stay<br>least 2 seconds then, t                                                                                                                                                                                                                                                                                                                                            | is true for at. Pa                |                 |              |                                       |                                   |                                                                     |

|                                                            |                            |                                                                          |                               |                                  | reast 2 seconds then, s                                                                                                                                                                                                                                                                                                                                                                     | untest                            |                 |              |                                       |                                   |                                                                     |

|                                                            |                            |                                                                          |                               |                                  | nsing edge of trigger, v<br>at most 2 seconds, put                                                                                                                                                                                                                                                                                                                                          | with a delay of                   | 0 5             | 10 15        | 20 25                                 | 30 35 40 45                       | 50 55 60 65                                                         |

20

? ×

**Create a Test Specification Report**

Test Specification Report

Title Page Information

Title:

Author

## **Measure completeness of testing**

#### **Model Verification**

- Manage requirements

- Check standard compliance

- Systematically test

- Measure model coverage

- Detect design errors

- Prove model behavior compliance

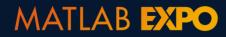

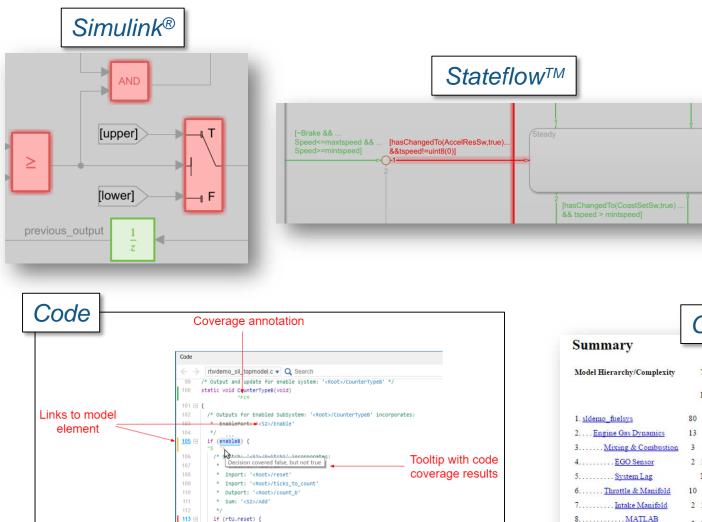

## **Coverage Analysis to Measure Testing**

114

rtY.count\_b = 0U;

- Identify testing gaps

- Missing requirements

- Unintended functionality

- Design errors

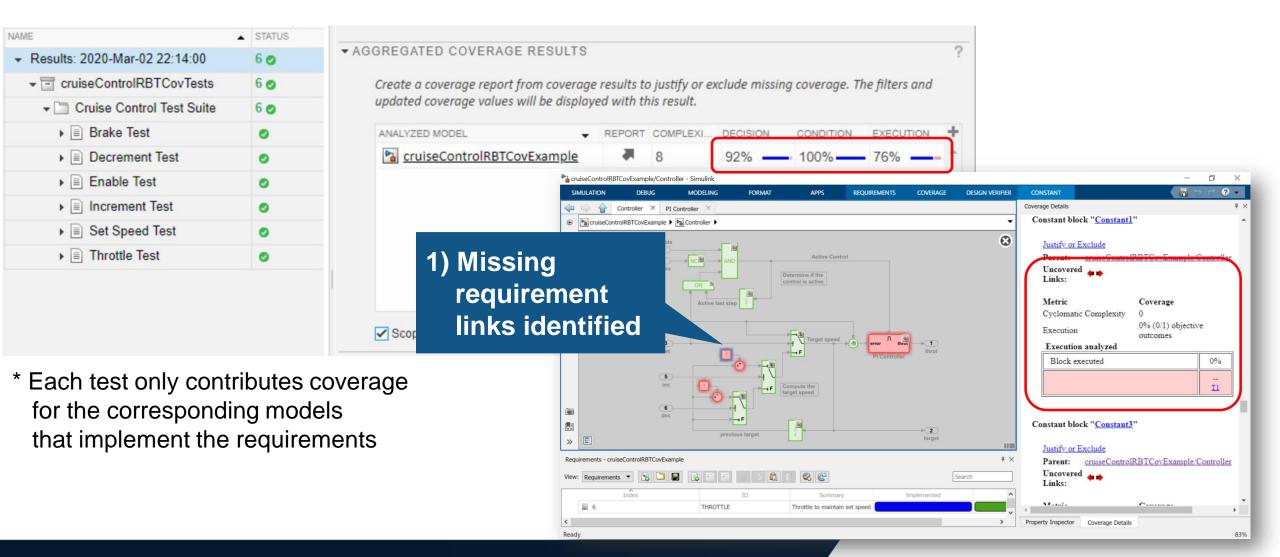

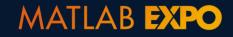

## **Test and Requirements Traceability in Coverage Results**

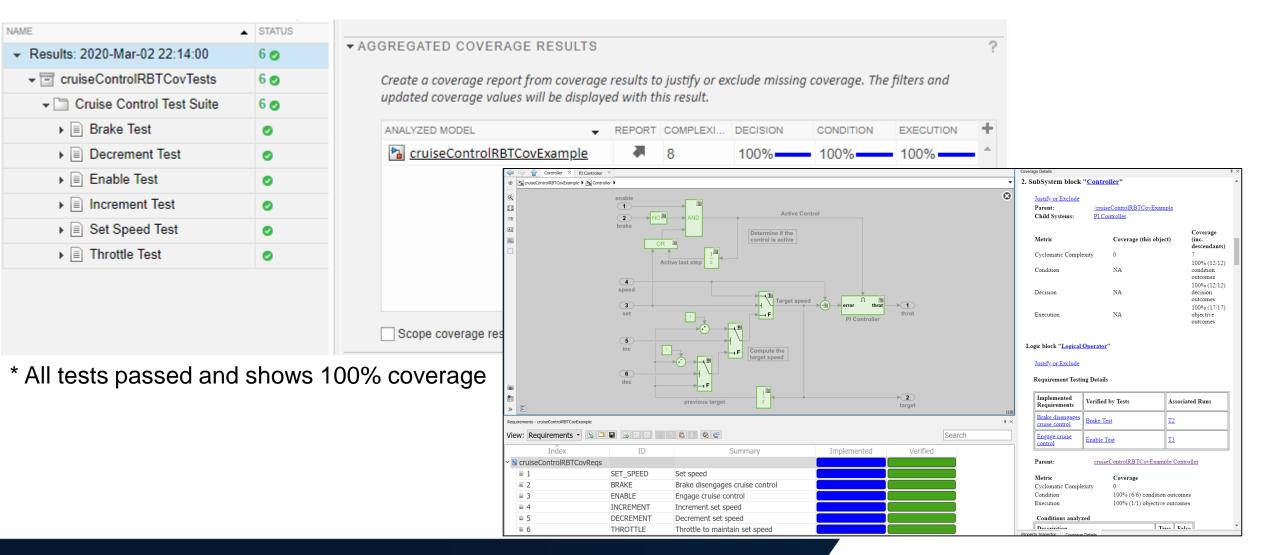

## **Scoping Model Coverage to Requirements-Based Tests**

| IAME 🔺                                            | STATUS |                                        |             |             |              |                |                             |        |

|---------------------------------------------------|--------|----------------------------------------|-------------|-------------|--------------|----------------|-----------------------------|--------|

| <ul> <li>Results: 2020-Mar-02 22:14:00</li> </ul> | 60     | ▼AGGREGATED COVERAGE RESULTS           | 5           |             |              |                |                             | 3      |

|                                                   | 6 🔿    | Create a coverage report from covera   |             |             | clude missir | ig coverage. T | he <mark>filters and</mark> | d      |

|                                                   | 60     | updated coverage values will be displo | ayed with t | his result. |              |                |                             |        |

| ▶                                                 | 0      | ANALYZED MODEL                         | REPORT      | COMPLEXI    | DECISION     | CONDITION      | EXECUTION                   | +      |

| <ul> <li>Decrement Test</li> </ul>                | 0      | CruiseControlRBTCovExample             |             | 8           | 92%          | 100%           | 76%                         | -      |

| ▶                                                 | 0      |                                        |             |             |              |                |                             |        |

| Increment Test                                    | 0      |                                        |             |             |              |                |                             |        |

| ▶                                                 | 0      |                                        |             |             |              |                |                             |        |

| ▶                                                 | 0      |                                        |             |             |              |                |                             |        |

|                                                   |        |                                        |             |             |              |                |                             | -      |

|                                                   |        |                                        |             |             |              |                |                             | 4      |

|                                                   |        | Scope coverage results to linked requ  | uirements   | >           | Add Tests f  | or Missing Cov | erage 🛛 🐺 E                 | export |

|                                                   |        |                                        |             |             |              |                |                             |        |

- Checking coverage of tests with the linked requirements

- 1) Testing(covered) with missing requirements

- 2) Testing(covered) with requirements but not by linked tests

- 3) Not testing(not covered)

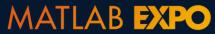

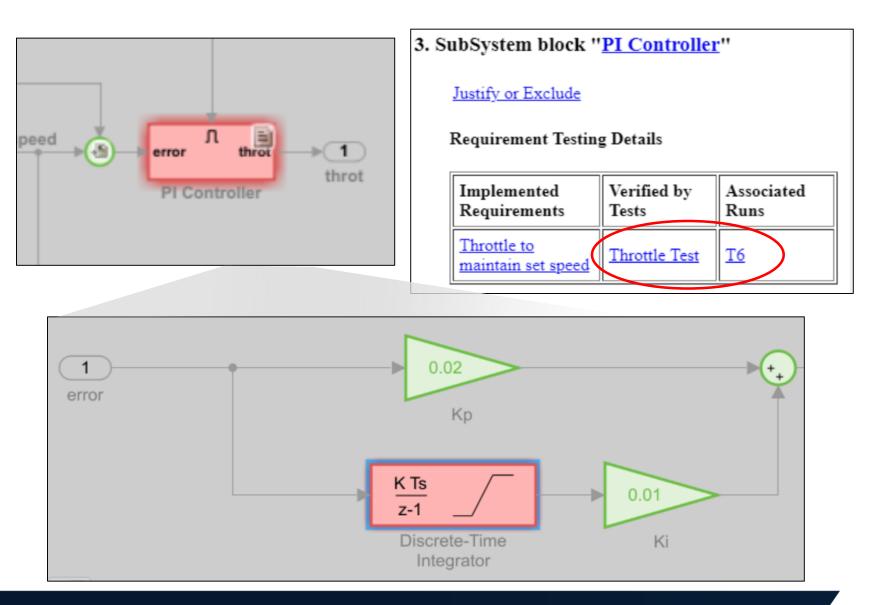

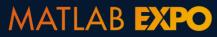

## **Scoping Model Coverage to Requirements-Based Tests**

## **Test and Requirements Traceability in Coverage Results**

## **Test and Requirements Traceability in Coverage Results**

## **Address missing Requirements-Based Test Coverage**

1) Add missing implementation links to requirements

2) Update test to increase target speed to be covered by the linked test

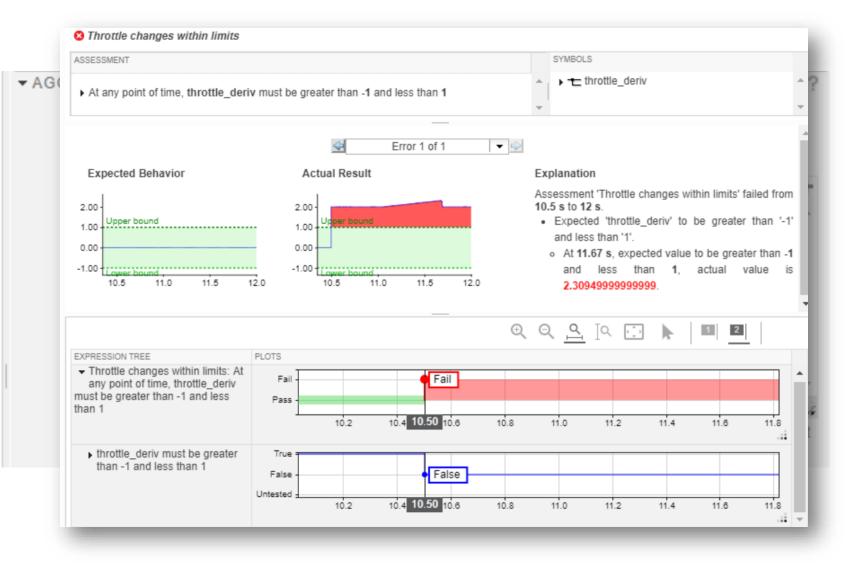

## **100% Coverage but Testing Identified Error in Implementation**

| ✓ Results: 2020-Mar-02 23:59:38              | 5 💿 1 😦 |

|----------------------------------------------|---------|

| <ul> <li>cruiseControlRBTCovTests</li> </ul> | 5 👩 1 👩 |

|                                              | 5 👩 1 👩 |

| Brake Test                                   | 0       |

| Decrement Test                               | 0       |

| Enable Test                                  | 0       |

| Increment Test                               | 0       |

| Set Speed Test                               | 0       |

| Throttle Test                                | 0       |

|                                              |         |

#### ▼ AGGREGATED COVERAGE RESULTS

Create a coverage report from coverage results to justify or exclude missing coverage. The filters and updated coverage values will be displayed with this result.

| ANALYZED MODEL                           | REPORT C | OMPLEXI            | DECISION           | CONDITION                                                    | EXECUTION +                            |

|------------------------------------------|----------|--------------------|--------------------|--------------------------------------------------------------|----------------------------------------|

| cruiseControlRBTCovExample               | <b>A</b> | 8                  | 100%               | 100%                                                         | 100%^                                  |

|                                          |          |                    | <u>or Exclude</u>  | "Discrete-Time Inte                                          | grator"<br>ample/Controller/PI Control |

|                                          |          | Decis<br>Execu     | matic Complexity   | <b>Coverage</b><br>2<br>100% (4/4) decis<br>100% (1/1) objec |                                        |

| Scope coverage results to linked require |          | egration result <= | 100%               |                                                              |                                        |

|                                          |          |                    | false              |                                                              | <u><u> </u></u>                        |

|                                          |          |                    | true               |                                                              | 556/950<br><u>T6</u>                   |

|                                          |          | inte               | egration result >= | upper limit                                                  | 100%                                   |

|                                          |          |                    | false              |                                                              | 950/1001<br>T6                         |

|                                          |          |                    | true               |                                                              | 51/1001<br><u>T6</u>                   |

|                                          |          |                    |                    | MathWork                                                     | S° 2                                   |

#### MATLAB **EXPO**

2

## **Additional Testing Identified Error in Implementation**

| ✓ Results: 2020-Mar-02 23:59:38              | 5 💿 1 😦 |

|----------------------------------------------|---------|

| <ul> <li>cruiseControlRBTCovTests</li> </ul> | 5 👩 1 👩 |

|                                              | 5 👩 1 😋 |

| Brake Test                                   | 0       |

| Decrement Test                               | 0       |

| Enable Test                                  | 0       |

| Increment Test                               | 0       |

| Set Speed Test                               | 0       |

| ▶                                            | 0       |

|                                              |         |

https://kr.mathworks.com/help/sltest/ug/test-coverage-for-requirements-based-testing.html?s\_tid=srchtitle

## **Scoped Model Coverage to Requirements-Based Tests**

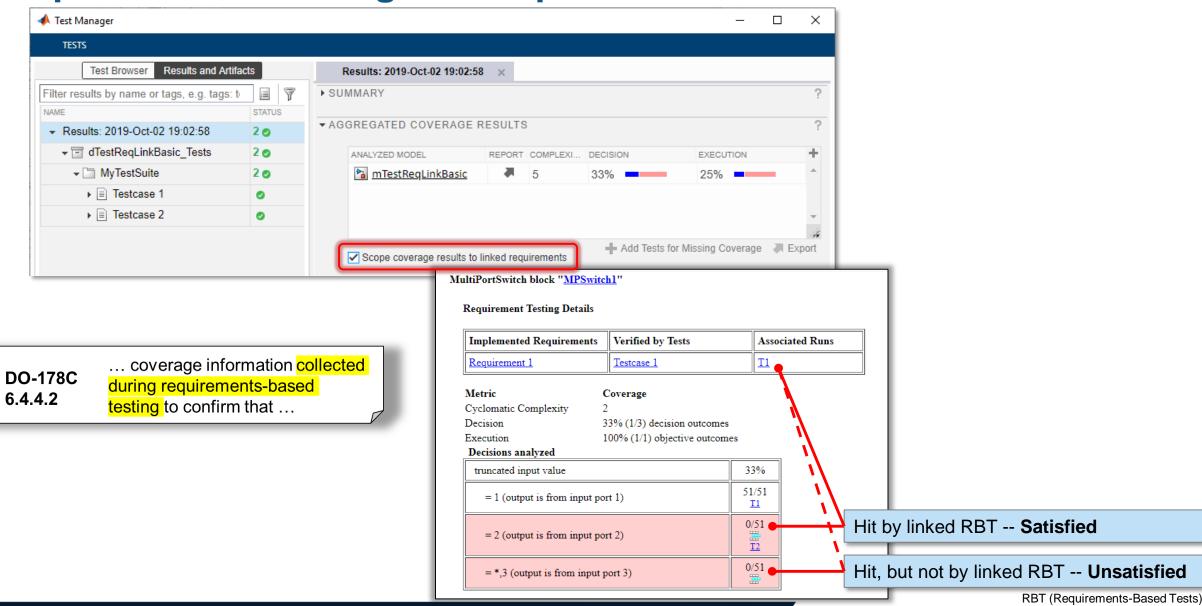

## **Check Standard Compliance**

#### **Model Verification**

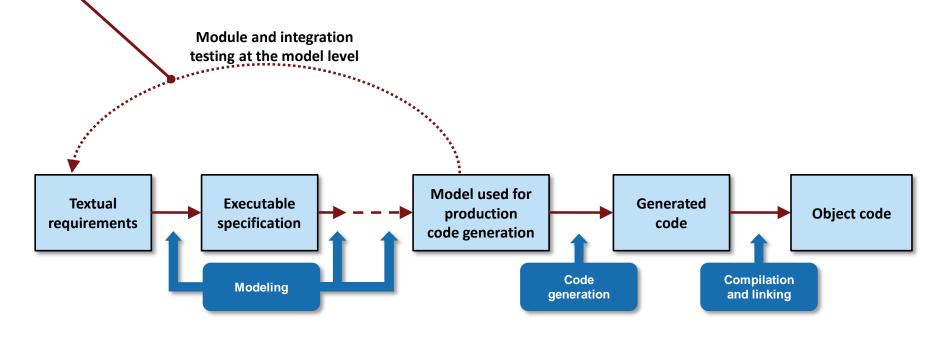

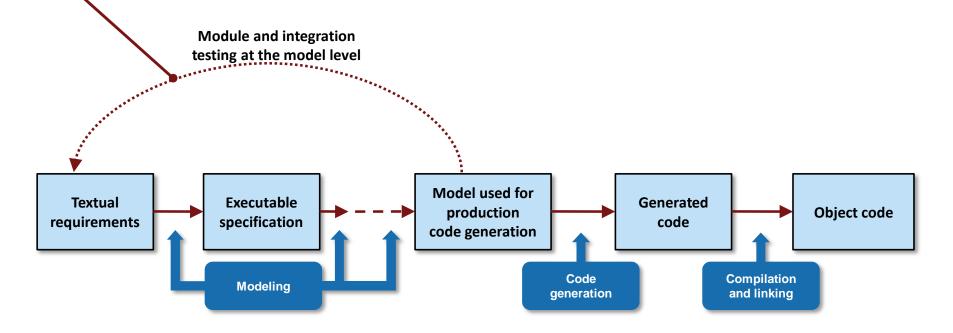

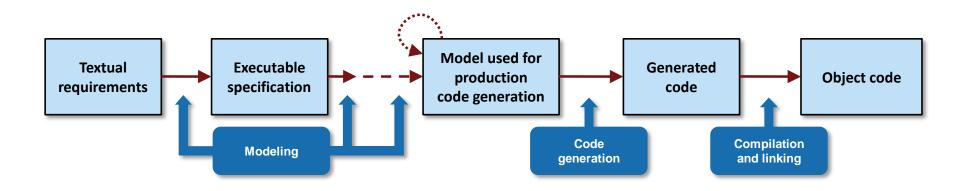

## **Verify Design to Guidelines and Standards**

Executable

specification

Modeling

Check for:

- Readability and Semantics

- Performance and Efficiency

- Clones (for optimization)

- And more.....

Compilation

and linking

Code

generation

Textual

requirements

## **Built in Checks for Industry Standards and Guidelines**

- DO-178/DO-331

MISRA C:2012

- ISO 26262 CERT C, CWE, ISO/IEC TS 17961

- IEC 61508

- IEC 62304

- EN 50128

- MAB (MathWorks Advisory Board)

- JMAAB (Japan MATLAB Automotive Advisory Board)

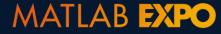

## **Shift Verification Earlier With Edit-Time Checking**

## **Detect Design Errors with Formal Methods**

### **Model Verification**

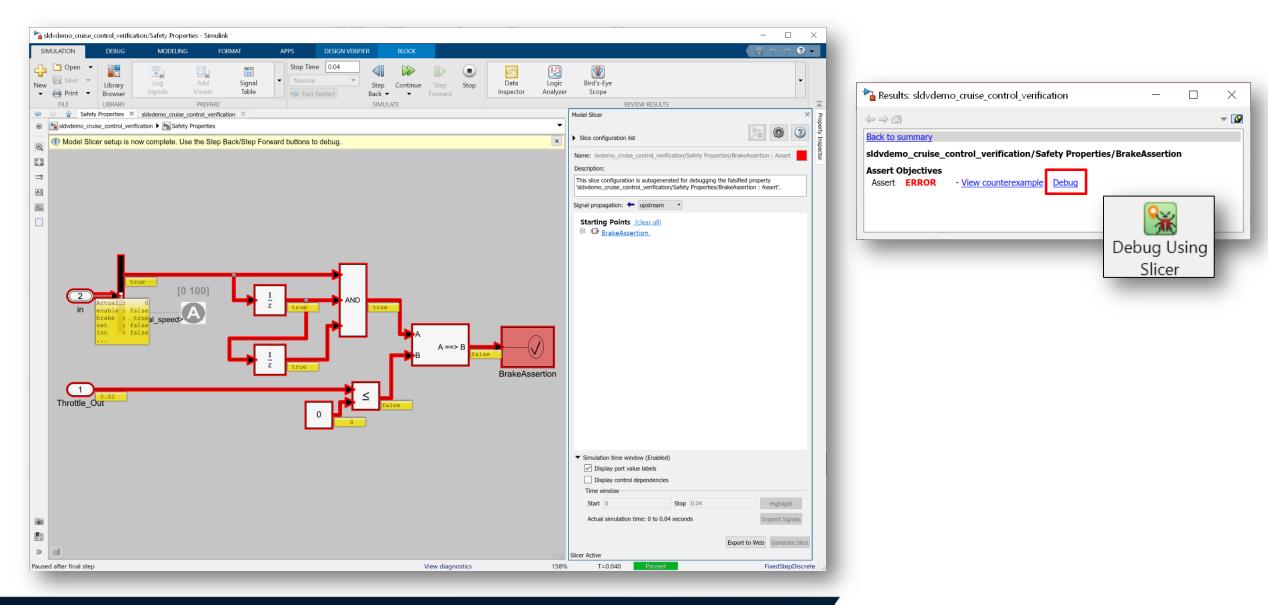

## **Detect Design Errors Using Formal Methods**

## **Prove Model Behavior Compliance**

## **Model Verification**

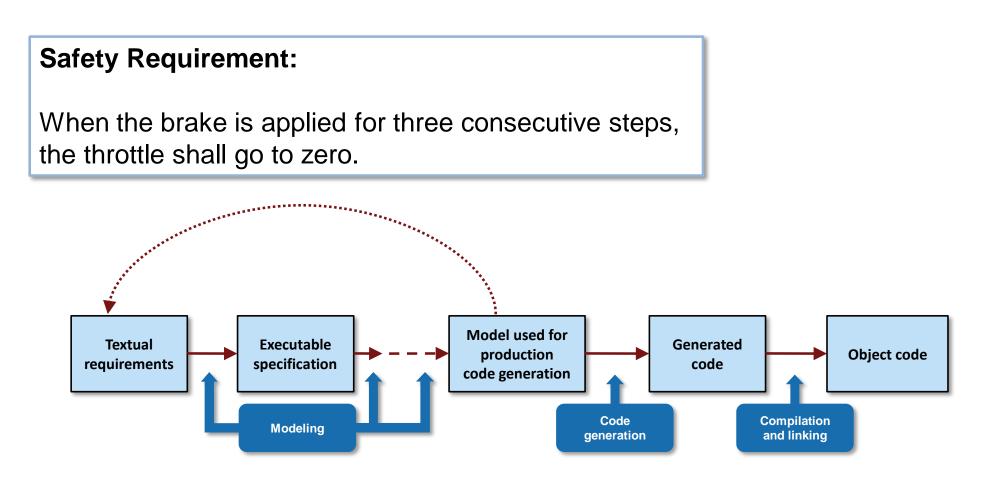

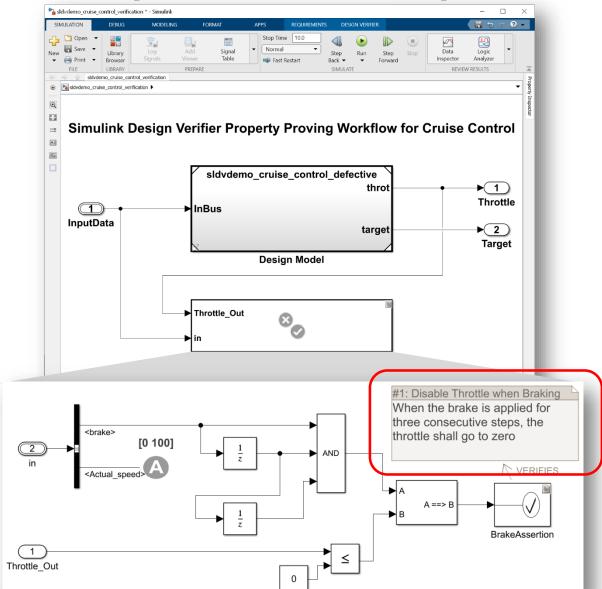

## **Proving Model Meets Requirements**

Need to ensure the design performs correctly

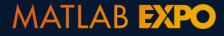

## **Model Functional and Safety Requirements**

https://kr.mathworks.com/help/sldv/ug/property-proving-workflow-for-cruise-control.html

## **Link Requirements to Properties**

MATLAB EXPO

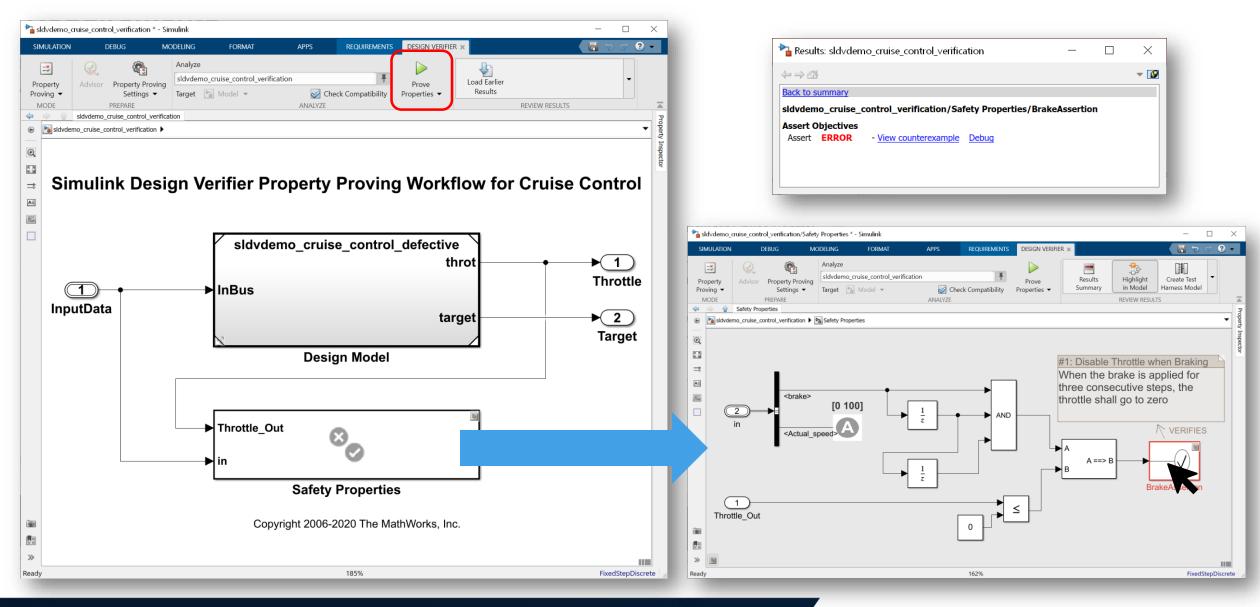

# **Prove That Design Meets Requirements**

## **Prove That Design Meets Requirements**

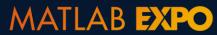

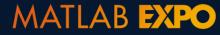

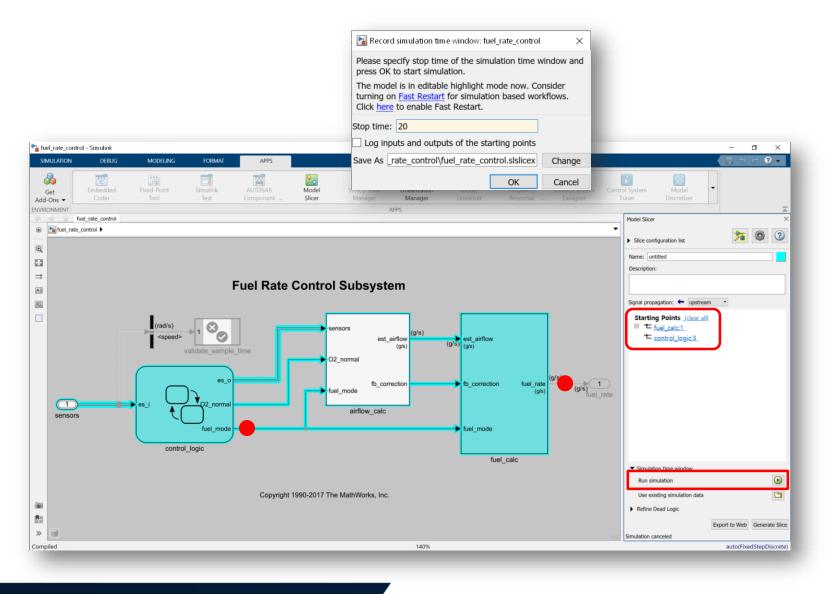

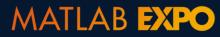

# **Debugging Property Proving Violations**

#### Isolate

Find the area of the model responsible for unexpected behavior

#### Isolate

Find the area of the model responsible for unexpected behavior

#### Analyze dependencies

Understand data & control dependencies in large or complex models

#### Isolate

Find the area of the model responsible for unexpected behavior

#### Analyze dependencies

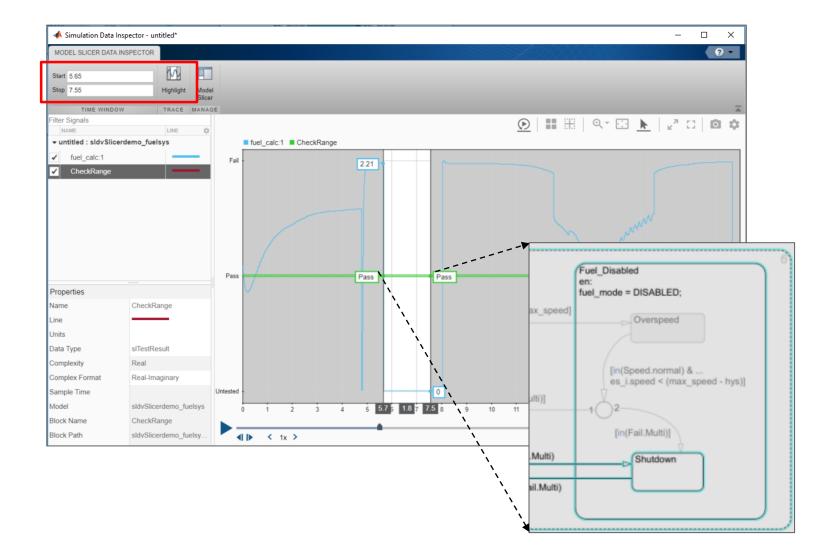

Understand data & control dependencies in large or complex models

#### **Inspect slice regions**

Highlight model slices for time windows or failure states & transitions for state flow.

#### Isolate

Find the area of the model responsible for unexpected behavior

#### Analyze dependencies

Understand data & control dependencies in large or complex models

#### **Inspect slice regions**

Highlight model slices for time windows or failure states & transitions for state flow.

#### Debug simulation behavior

Step through precompiled slices to understand signal and port value propagation

#### **Correct Model**

## MATLAB **EXPO**

## **Code Verification: Gain Confidence in the Generated Code**

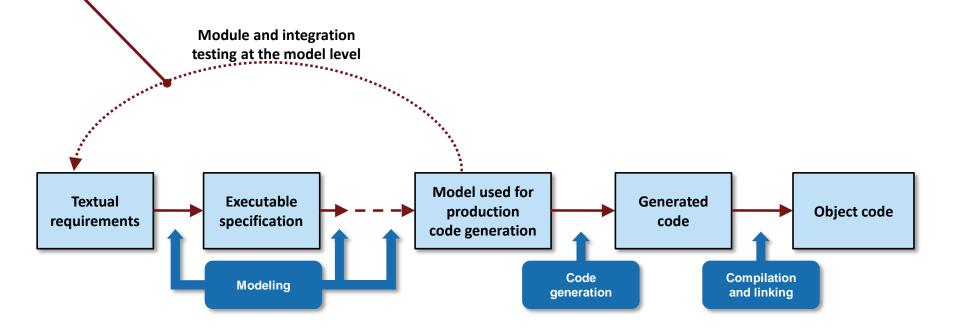

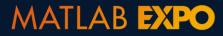

## **Back-to-Back Testing: Simulation-In-the-Loop**

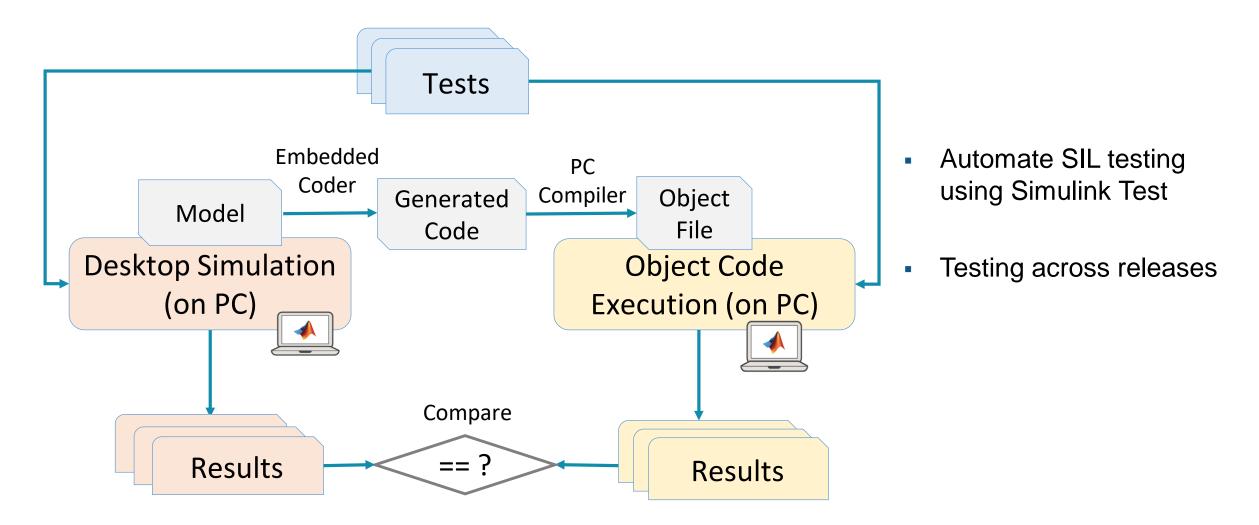

## **Back-to-Back Testing: Processor-In-the-Loop**

## **Automate Test Creation using Test Manager Wizard**

- Guided steps to define component to test, inputs, type of test and format for output

- Wizard generates required test harness

- Auto generate tests using Simulink **Design Verifier**

| 📣 Test Manager                                                                                                                                                        | Create Test for Model Component                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TESTS DATA INSPECTOR FORMAT                                                                                                                                           | System > Test Inputs > Verification Strategy > Generated Test                                                                                                                                                                                                                                                                   |

| New     Open     Save     Copy     Delete     Test Spec     Run       Test File     Create a blank test file       Test Suite       Create a container for test cases | What is your Component under Test (CUT)? Top Mode Create Test for Model Component Compone System > Test Inputs > Verification Strategy > Generated Test                                                                                                                                                                         |

| TEST CASE TEMPLATES Baseline Test Compare simulation output to a fixed baseline signal Equivalence Test Compare output of two simulations Simulation Test             | How do you want to set up the inpute?                                                                                                                                                                                                                                                                                           |

| Perform a simulation with no criteria Real-Time Test Perform a simulation on real-time target AUTO CREATE Test File from Model                                        | Create a       Ouse component under test output as baseline         Simulate the top model and record the outputs of the component to be used as baseline         Perform back-to-back testing         Set up a test to compare the component under test outputs in different simulation modes         Select simulation modes: |

| Create a test file from model Test for Model Component Create a new baseline or back-to-back test for model component                                                 | Simulat System > Test Inputs > Verification Strategy > Generated Test                                                                                                                                                                                                                                                           |

| Test from Spreadsheet<br>Create a new test with data specified in a spreadsheet                                                                                       | O Define th         No verifi         Specify the format to save the test data:         EXCEL         Specify the location to save the test data:         B2BtestData                                                                                                                                                           |

### MATLAB EXPO

## **Automate Test Creation using Test Manager Wizard**

📣 Test Manager

New

- Guided steps to define component to test, inputs, type of test and format for output

- Wizard generates required test harness

- Auto generate tests using Simulink **Design Verifier**

| 📣 Test Manager                                                                            |                                                                                                   |  |  |  |  |  |

|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--|--|--|--|--|

| TESTS DATA INSPECTOR FORMAT                                                               | rtudeme eil bleck Herneset                                                                        |  |  |  |  |  |

| 🔓 🔄 🔚 💰 Cut 🗊 🌗 🕨                                                                         | rtwdemo_sil_block_Harness1                                                                        |  |  |  |  |  |

| New Open Save Copy Delete Test Spec Rur                                                   | rr B2Btest » New Test Suite 1 » rtwdemo sil block Harness1                                        |  |  |  |  |  |

| • • • 🖓 Paste • Report •                                                                  | Equivalence Test                                                                                  |  |  |  |  |  |

| File Select releases for simulation: Current -                                            |                                                                                                   |  |  |  |  |  |

| Create a blank test file                                                                  | ▼ DESCRIPTION*                                                                                    |  |  |  |  |  |

| Test Suite<br>Create a container for test cases                                           | Test generated for the subsystem 'rtwdemo_sil_block/Controller'.                                  |  |  |  |  |  |

| TEST CASE TEMPLATES                                                                       | ▼ SIMULATION 1                                                                                    |  |  |  |  |  |

| Baseline Test<br>Compare simulation output to a fixed baseline signal                     | ▼ SYSTEM UNDER TEST*                                                                              |  |  |  |  |  |

| Equivalence Test                                                                          | Model: rtwdemo_sil_block                                                                          |  |  |  |  |  |

| Compare output of two simulations                                                         | ▼ TEST HARNESS*                                                                                   |  |  |  |  |  |

| Simulation Test<br>Perform a simulation with no criteria                                  | Harness: rtwdemo_sil_block_Harness1                                                               |  |  |  |  |  |

| Real-Time Test                                                                            | ▼ SIMULATION SETTINGS OVERRIDES*                                                                  |  |  |  |  |  |

| Perform a simulation on real-time target                                                  | Simulation Mode: Normal   Override model blocks in SIL/PIL mode to normal mode                    |  |  |  |  |  |

| AUTO CREATE                                                                               |                                                                                                   |  |  |  |  |  |

| Test File from Model                                                                      | ✓ SIMULATION 2 Copy settings from Simulation 1                                                    |  |  |  |  |  |

| Create a test file from model                                                             | ▼SYSTEM UNDER TEST*                                                                               |  |  |  |  |  |

| Test for Model Component<br>Create a new baseline or back-to-back test for model componer | Model: rtwdemo_sil_block                                                                          |  |  |  |  |  |

| Test from Spreadsheet<br>Create a new test with data specified in a spreadsheet           | ▼ TEST HARNESS*                                                                                   |  |  |  |  |  |

| Greate a new test with data specified in a spreadsfiller                                  | Harness: rtwdemo_sil_block_SILHarness1                                                            |  |  |  |  |  |

|                                                                                           | ▼ SIMULATION SETTINGS OVERRIDES*                                                                  |  |  |  |  |  |

|                                                                                           | Simulation Mode: Software-in-the-Loop (SIL)  Override model blocks in SIL/PIL mode to normal mode |  |  |  |  |  |

## **Cross Release SIL/PIL Test Harness Generation**

- Create a SIL/PIL test harness using code that was generated in a previous release

- Modify existing SIL/PIL test harnesses to store the build folder path information which can be used for rebuild

| ■       Amplifier0_ert_rtw         ●       html         ●       html         ●       Amplifier0_comp.rsp         ●       Amplifier0_ref.rsp         ●       Amplifier0.bat         ●       Amplifier0.h         ●       Amplifier0.h         ●       Amplifier0.nk         ●       Amplifier0.rsp         ●       Amplifier0.rsp         ●       buildInfo.mat         ○       codelescriptor.dmr         ●       codelenfo.mat         ●       compileInfo.mat         ○       ert_main.cbj         ●       modelsources.txt         □       rtw_proj.tmw         ●       setup_msvc150.bat | Specify the properties of the test harness. The component under test is the system for which the harness is being created. After creation, use the block badge to find and open harnesses.         Component under Test:       mtwdemo_counter/Amplifier         Basic Properties       Advanced Properties       Description         Harness Creation Options       Verification Mode:       Software-in-the-Loop (SIL)         Use generated code to create SIL/PIL block       Build folder:       H'\Simulink Test\SILHarness\Internal_Demos\Amplifier0_ert_rtw       Browse         Post-create callback method | 1<br>2<br>equal_to_count<br>Trigger<br>Signal spec.<br>and routing | Signal spec.<br>and routing |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------|

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------|

## **Use Reference Workflow to Conform to Standards**

- Shift verification earlier

- Automate manual verification tasks (coding, compiling, back-to-back)

- Measure completeness of Requirements-Based Testing

## **Customer References and Applications**

Airbus Helicopters Accelerates Development of DO-178B Certified Software with Model-Based Design

Software testing time cut by two-thirds

LS Automotive Reduces Development Time for Automotive Component Software with Model-Based Design

Specification errors detected early

Continental Develops Electronically Controlled Air Suspension for Heavy-Duty Trucks

Verification time cut by up to 50 percent

More User Stories: https://kr.mathworks.com/company/user stories.html

- Verification, Validation, and Test Solution Page

- <u>Requirements-Based Testing Workflow Example</u>

- Verifying Models and Code for High-Integrity Systems

- Getting Started with Model Verification and Validation of the sector of t

- 모델과 코드의 표준 적합성을 점검하고 품질을 측정합니다.

- 자동으로 테스트 케이스를 생성하여 테스트 커버리지를 확대합니다

- 보고서와 아티팩트를 생성하고 표준 적합성을 인증합니다(DO-178 및 ISO 26262 등

– Daming Li, Weichai Power

# Thank You !!