## MATLAB EXPO 2016 KOREA

4월 28일 (목)

등록 하기 matlabexpo.co.kr

## MATLAB과 Simulink를 이용한 프로그래머블 SoC 설계

**Application Engineering Group**

© 2016 The MathWorks, Inc.

#### Agenda

#### Introduction

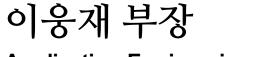

- What is Zynq?

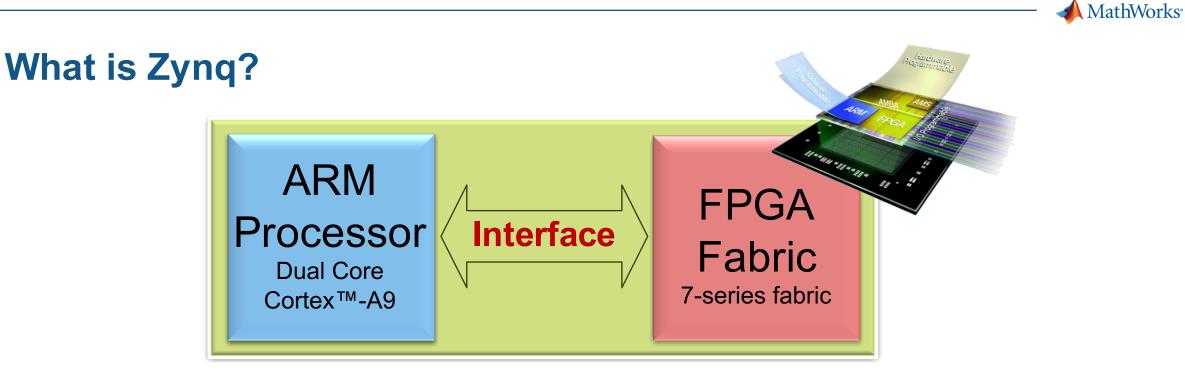

- Design Challenges

- ZYNQ Design Process

- MBD on Programmable SoC

- Code Generation

- Workflow

- Verification & Partitioning

- Parameter Tuning

- UDP Interface

- Processor In the Loop

- Advanced Features

- Conclusions

#### SEPTEMBER NEWSLETTER E XILINX > AL INXX **Top Story** artin A. Enderwitz Zyng Book Reaches Top-10 B The Zyng Book, written by a tear 🕅 /de, Glasgow, UK, is already a treme ROOK status on Amazon.com in severa -on, Embedded Processing with the ARM<sup>®</sup> Cortex<sup>®</sup>-A9 comprehensive guide to using X and on the Xilinx® Zynq®-7000 All Programmable SoC covers all aspects development : implementation. The book also fe E XILINX more, it is a free PDF download! able University of Strathclyde Glasgow price. Get the free PDF download » In association with Buy a hard copy on Amazon.cor Learn more about the Zyng SoC

- New product family from Xilinx<sup>®</sup>

- All Programmable System on Chip (SoC)

- FPGA Fabric + ARM<sup>®</sup> on one a single chip

- Enables high-performance system development

- Reduces BOM cost over multi-chip solutions

- **FPGA Designers** not familiar with programming processors

- **DSP/Processor programmers** not familiar with FPGAs

- What should run on the FPGA vs. what should run on the ARM?

- No established rules for hooking up the interface between FPGA and ARM processor

# How can I address these challenges and get my project onto Zynq quickly?

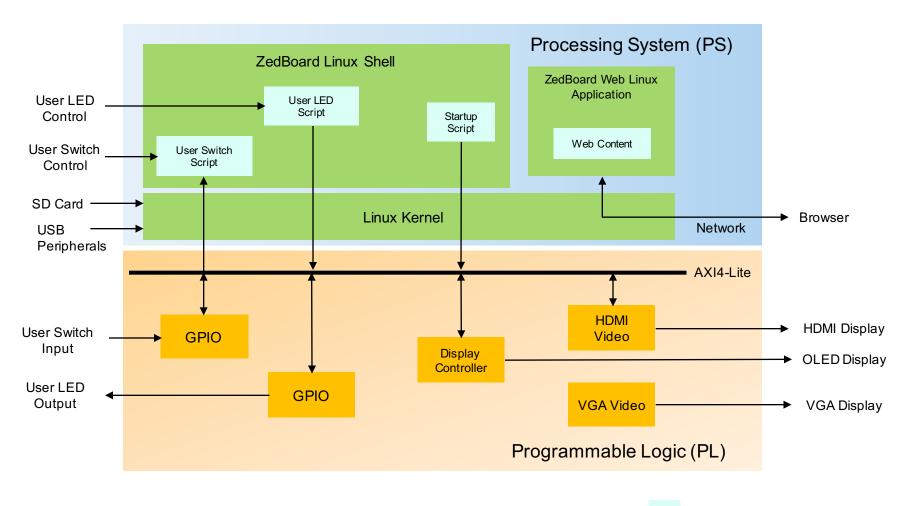

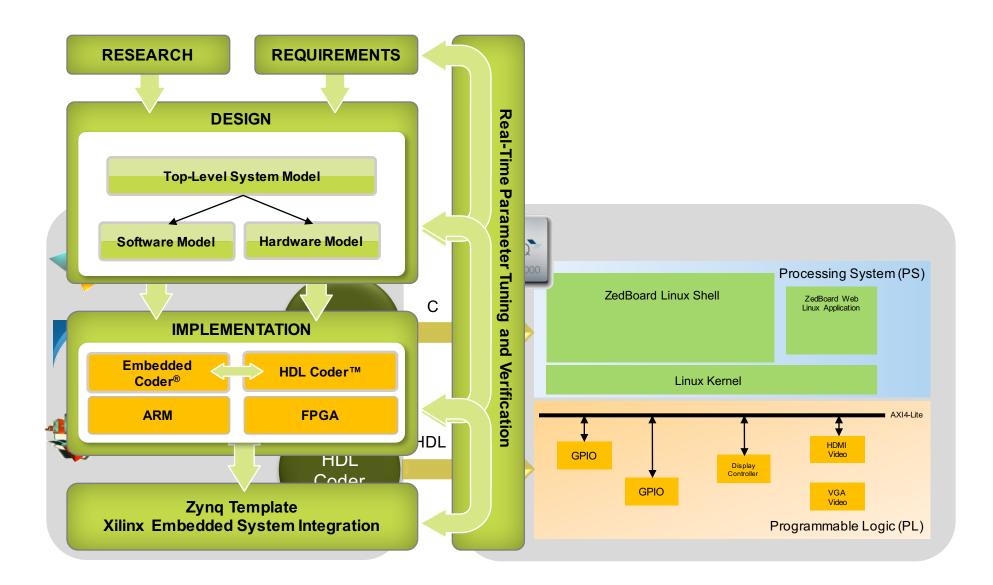

- Model-Based Design provides a single environment from requirements to prototype seamlessly

- A guided workflow for hardware and software development

#### Hardware platform to prototyping

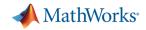

- Board Name: ZedBoard<sup>™</sup>

Zynq-7000 AP SoC XC7Z020-CLG484

- Memory:

- ✓ 512 MB DDR3

- ✓ 256 Mb Quad-SPI Flash

- ✓ 4 GB SD card

- Onboard USB-JTAG Programming

- 10/100/1000 Ethernet

- USB OTG 2.0 and USB-UART

- PS & PL I/O expansion (FMC, Pmod<sup>™</sup>, XADC)

- Multiple displays (1080p HDMI, 8-bit VGA, 128 x 32 OLED)

- I<sup>2</sup>S Audio CODEC

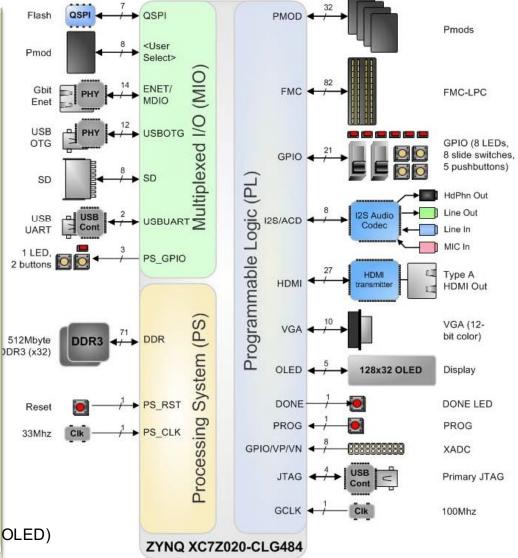

#### System configuration for prototyping

Drivers/Application Examples (Linux)

Programmable Logic IP

#### **Support Package Installer**

| Support Packa<br>lect a suppor | t package to install       |                      |                   |                               |                                           | lp | Request Support                              |

|--------------------------------|----------------------------|----------------------|-------------------|-------------------------------|-------------------------------------------|----|----------------------------------------------|

| Action                         | Support Package for        | Installed<br>Version | Latest<br>Version | Required Base Product         | Supported Host Platforms                  | r  | Add-Ons 👻                                    |

| 🚺 Install                      | Arduino                    |                      | 3.0               | Simulink                      | Windows (32-bit), Windows (64-bit)        |    | Get More Apps                                |

| Install                        | BeagleBoard                |                      | 3.0               | Simulink                      | Windows (32-bit), Windows (64-bit)        |    | Get More Apps<br>Get Apps from File Exchange |

| Install                        | Gumstix Overo              |                      | 1.0               | Simulink                      | Windows (32-bit), Windows (64-bit)        |    | Get Apps from the Exchange                   |

| Install                        | LEGO MINDSTORMS NXT        |                      | 3.0               | Simulink                      | Windows (32-bit), Windows (64-bit)        |    |                                              |

| Install                        | PandaBoard                 |                      | 3.0               | Simulink                      | Windows (32-bit), Windows (64-bit)        |    | Get Hardware Support Pac                     |

| Install                        | Raspberry Pi               |                      | 3.0               | Simulink                      | Windows (32-bit), Windows (64-bit)        |    | Find and install hardware                    |

| Install                        | USRP(R) Radio              |                      | 5.0               | Communications System Toolbox | Windows (32-bit), Windows (64-bit), Linu  |    |                                              |

| Install                        | Xilinx FPGA-Based Radio    |                      | 1.0               | Communications System Toolbox | Windows (32-bit), Windows (64-bit), Linu  |    |                                              |

| Install                        | ARM Cortex-M               |                      | 1.0               | DSP System Toolbox            | Windows (32-bit), Windows (64-bit), Linu  |    | Get MathWorks Products                       |

| Install                        | Digilent Analog Discovery  |                      | 1.0               | Data Acquisition Toolbox      | Windows (32-bit), Windows (64-bit)        |    | View and download Math                       |

| Instal                         | Analog Devices DSPs        |                      | 2.0               | Embedded Coder                | Windows (32-bit), Windows (64-bit)        |    |                                              |

| Install                        | Green Hills MULTI          |                      | 3.0               | Embedded Coder                | Windows (32-bit), Windows (64-bit), Linu  |    | Charle (an Deadlach Harles                   |

| Install                        | Texas Instruments TL C2000 |                      | 2.0               | Embedded Coder                | Windows (32-bit), Windows (64-bit), Linu  |    | Check for Product Updates                    |

| - Instal                       | Xilinx Zynq-7000           |                      | 1.0               | Embedded Coder                | Windows (32-bit), Windows (64-bit)        |    |                                              |

| Instal                         | Xilinx Zynq-7000           |                      | 1.0               | HDL Coder                     | Linux (64-bit), Windows (32-bit), Windows |    |                                              |

| Install                        | Altera FPGA boards         |                      | 2.0               | HDL Verifier                  | Linux (04-bit), windows (32-bit), Window  |    |                                              |

| Install                        | Xilinx FPGA Boards         |                      | 2.0               | HDL Verifier                  | Linux (64-bit), Windows (32-bit), Window  |    |                                              |

| Install                        | Kinect for Windows Runtime |                      | 1.6               | Image Acquisition Toolbox     | Windows (32-bit), Windows (64-bit)        |    |                                              |

| Install                        | NI-Fgen                    |                      | 1.0               | Instrument Control Toolbox    | Windows (32-bit), Windows (64-bit)        |    |                                              |

| Install                        | NI-Scope                   |                      | 1.0               | Instrument Control Toolbox    | Windows (32-bit), Windows (64-bit)        |    |                                              |

|                                | Ocean Optics Spectrometers |                      | 1.0               | Instrument Control Toolbox    | Windows (32-bit),Windows (64-bit),Linu    |    |                                              |

| Install                        | BitFlow NEON CL            |                      | 2.0               | xPC Target                    | Windows (32-bit), Windows (64-bit)        |    |                                              |

| Install                        | USB Video                  |                      | 2.0               | xPC Target                    | Windows (32-bit), Windows (64-bit)        |    |                                              |

#### Agenda

#### Introduction

- What is Zynq?

- Design Challenges

- ZYNQ Design Process

- MBD on Programmable SoC

- Code Generation

- Workflow

- Verification & Partitioning

- Parameter Tuning

- UDP Interface

- Processor In the Loop

- Advanced Features

- Conclusions

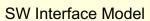

#### **Model-Based Design for Zynq**

#### **Model-Based Design for Zynq**

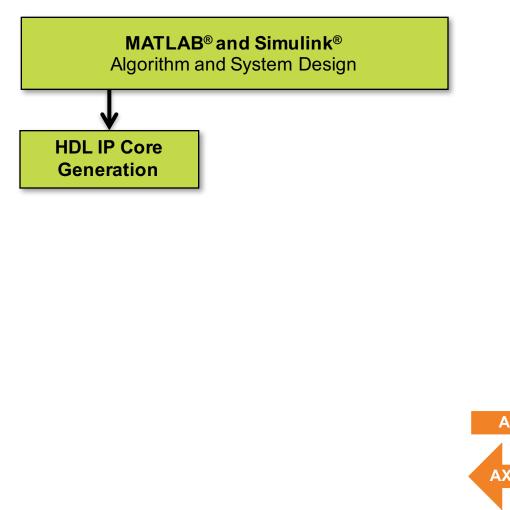

#### **Code Generation Scheme**

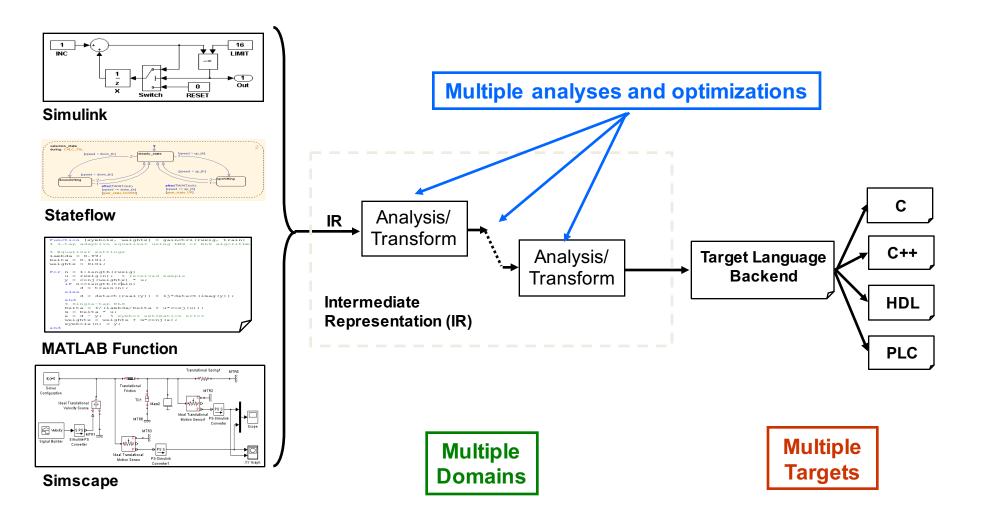

#### Multi-Domain, Multi-Target Technology

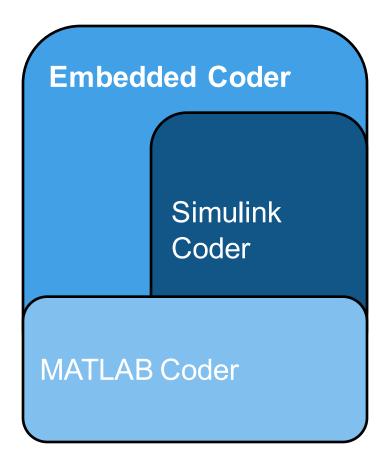

#### **Code Generation Products for C/C++**

Embedded Coder<sup>™</sup> Automatically generate C and C++ optimized for embedded systems

Simulink<sup>®</sup> Coder<sup>™</sup> Automatically generate C and C++ from **Simulink** models and **Stateflow** charts

MATLAB<sup>®</sup> Coder<sup>™</sup> Automatically generate C and C++ from **MATLAB** code

#### **Optimize the C/C++ code for performance**

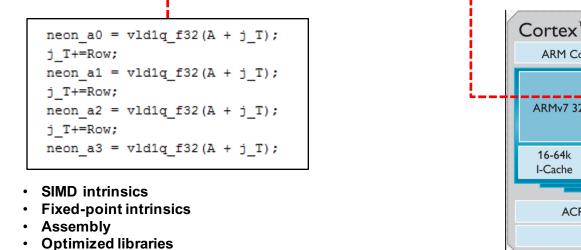

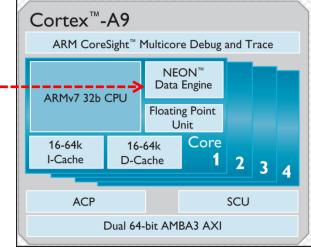

- 1. Optimize the generated C/C++ code

- 2. Use the ARM NEON Media Processing Engine

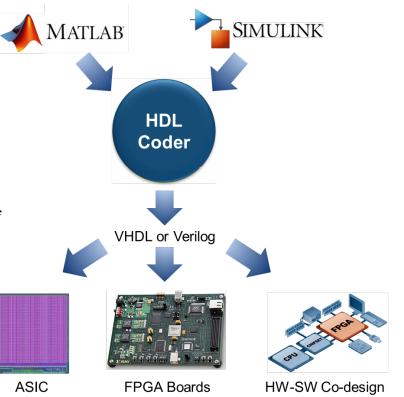

#### **Code Generation Products for VHDL/Verilog**

HDL Coder

MATLAB Coder

HDL Coder<sup>™</sup> Automatically generate synthesizable RTL code (VHDL or Verilog) from **MATLAB** code and **Simulink** Model

MATLAB<sup>®</sup> Coder<sup>™</sup> Automatically generate C and C++ from **MATLAB** code

#### **HDL Coder Key Features**

- Code Generation

- Target-independent Synthesizable RTL Code

- IEEE 1376 compliant VHDL®

- IEEE 1364-2001 compliant Verilog®

- Verification

- Generate HDL test-bench

- Co-simulate with ModelSim and Incisive\*

- Design automation

- Synthesize using integrated Xilinx and Altera synthesis tool interface

- Optimize for area-speed

- Program Xilinx and Altera boards

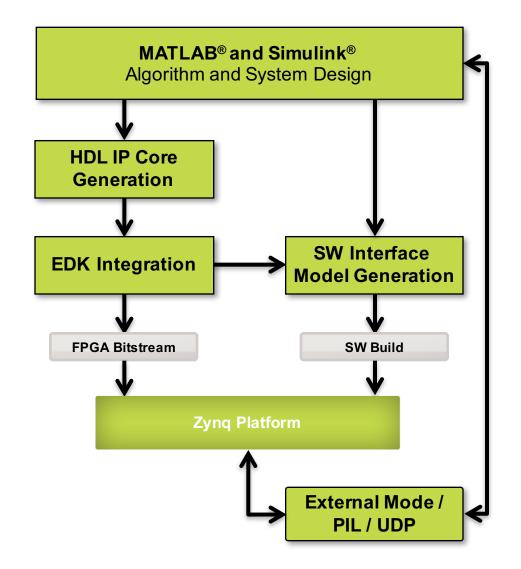

- Real-time Parameter Tuning and Verification

- External Mode

- Processor-in-the-loop

- UDP

- More probe and debug capability in the future

#### Agenda

- Introduction

- What is Zynq?

- Design Challenges

- ZYNQ Design Process

- MBD on Programmable SoC

- Code Generation

- Workflow

- Verification & Partitioning

- Parameter Tuning

- UDP Interface

- Processor In the Loop

- Additional Features

- Conclusions

#### **Verification Challenges:**

- Design the test bench twice

- 10 to 1 ratio of Test bench LOC to Design LOC (for HDL)

- Many stimuli-files from MATLAB

- How to analyze results?

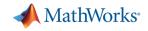

#### **Parameter tuning through External Mode**

- Tuning model parameters and <u>evaluate the effects of</u> <u>different parameter</u> values on model results in real time.

- Helping you find the optimal values to achieve desired performance.

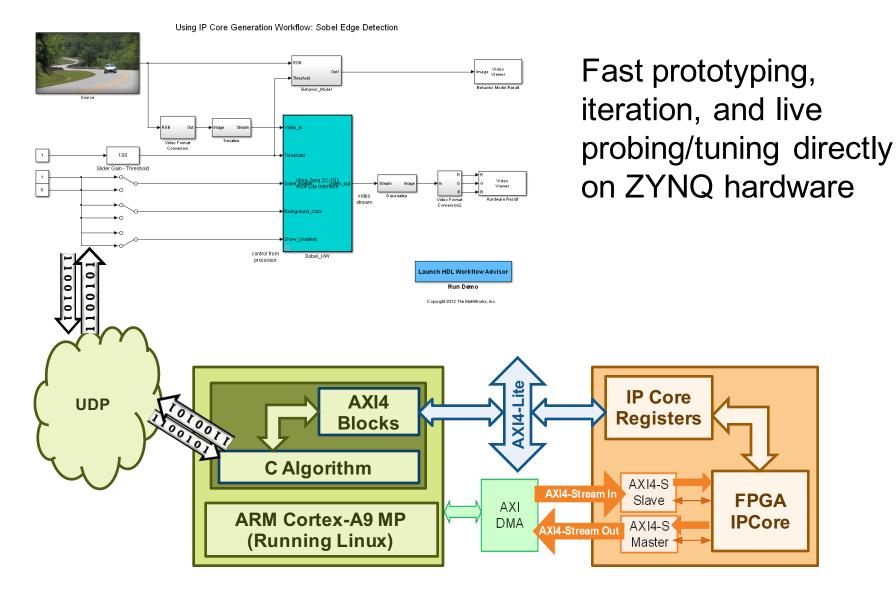

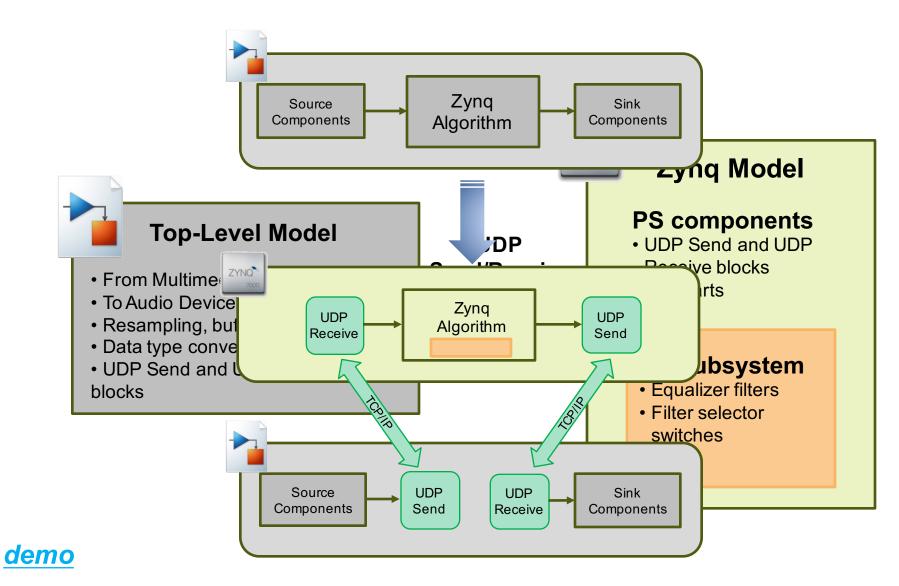

#### **Verification through UDP Interface**

#### **Design Partitioning for UDP**

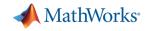

#### **Processor-In-the Loop(PIL) Verification**

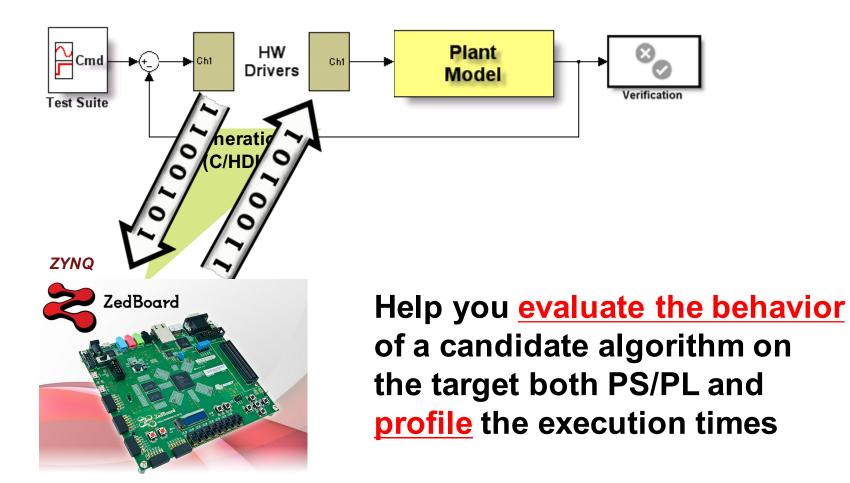

#### **Partitioning Scheme via PIL**

#### **Verification Tradeoffs**

| Feature              | External Mode   | PIL        | UDP             |

|----------------------|-----------------|------------|-----------------|

| Real-time execution  | √Yes            | ×No        | √Yes            |

| Parameter tuning     | √Yes            | ×No        | ×No             |

| Test bench options   | <b>×Limited</b> | ✓Unlimited | ✓Unlimited      |

| Code verification    | ×No             | √Yes       | ×No             |

| Execution profiling  | ×No             | √Yes       | ×No             |

| Single model         | √Yes            | √Yes/No    | ×No             |

| Data synchronization | <b>×Limited</b> | √Yes       | <b>×Limited</b> |

#### Agenda

- Introduction

- What is Zynq?

- Design Challenges

- ZYNQ Design Process

- MBD on Programmable SoC

- Code Generation

- Workflow

- Verification & Partitioning

- Parameter Tuning

- UDP Interface

- Processor In the Loop

- Advanced Features

- Conclusions

#### **Recently updated features in R2015a/R2015b**

#### ▶ R2015a

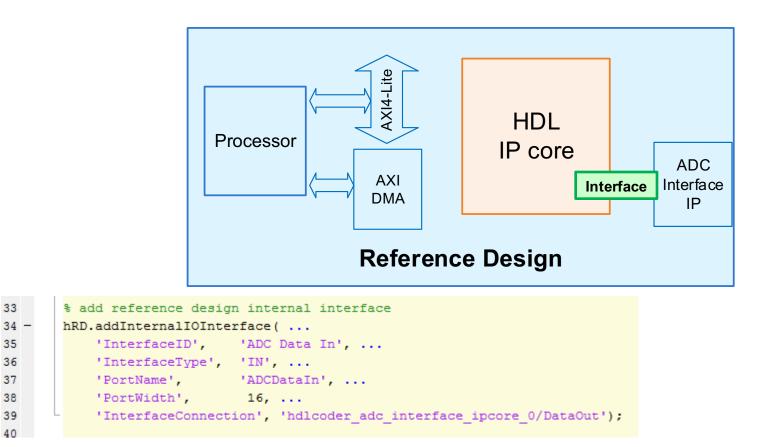

- <u>Internal-interface API in custom reference design</u>

- Zynq AXI Stream support

- Support Front Digital IO of Speedgoat IO331 board

- Save target setting as model properties

#### > R2015b

- <u>Command-line API for WFA</u>

- Export/Import between API and WFA

- Map tunable parameters to AXI interfaces

- <u>A</u>XI stream vector mode

- Internal-interface API in custom reference design

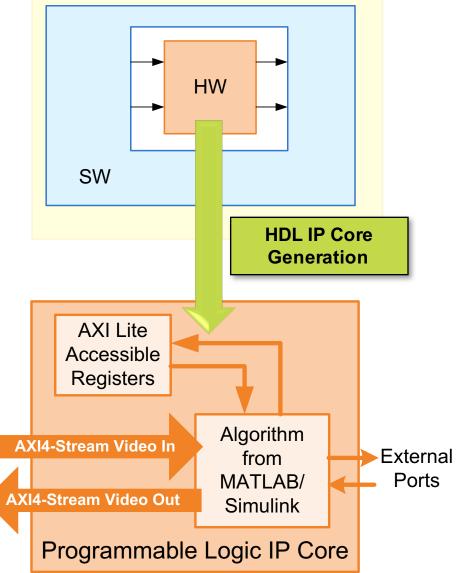

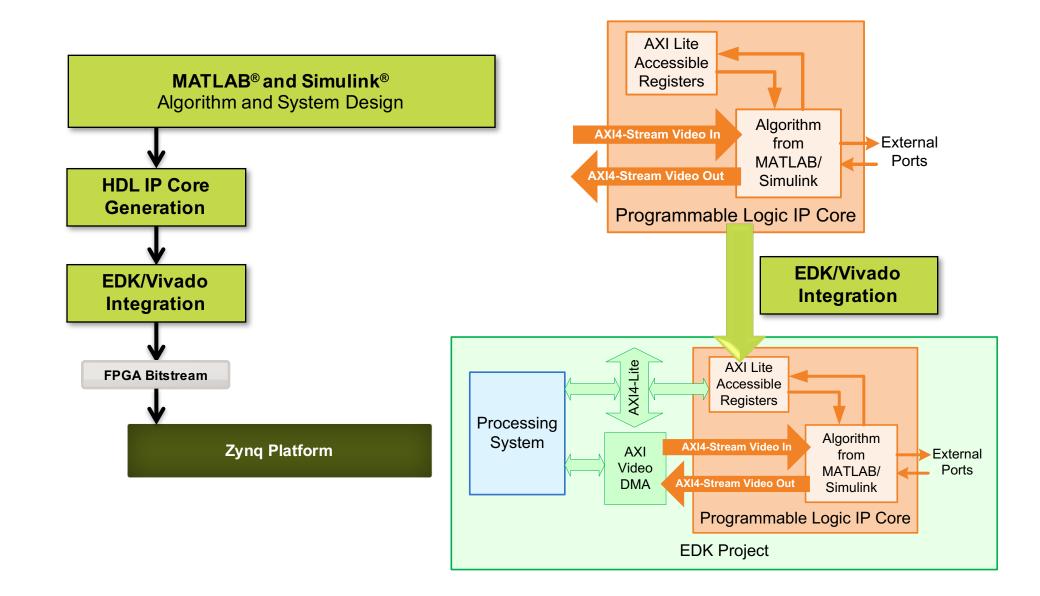

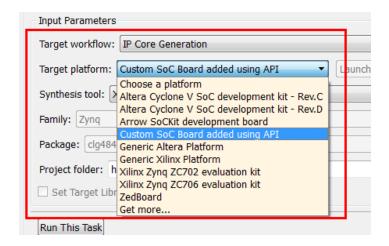

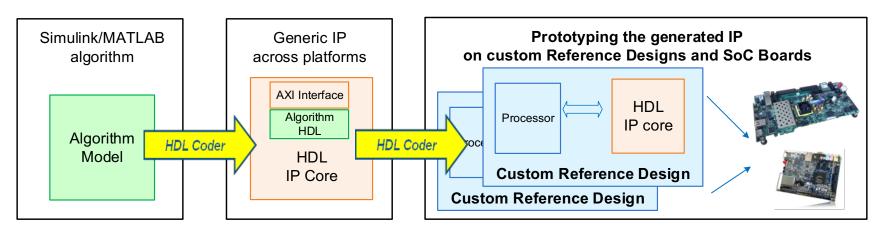

## Custom Board and Reference Design API for IP Core Generation Workflow

#### Define your own Zynq or Altera SoC Board and Reference Design

- Enable fast on-board prototyping and iteration

- Access to SW interface model generation, AXI driver, External Mode

## Custom Reference design API extension R2015b for Internal Interface

- Define an interface that connects to another IP in the reference design

R2015a

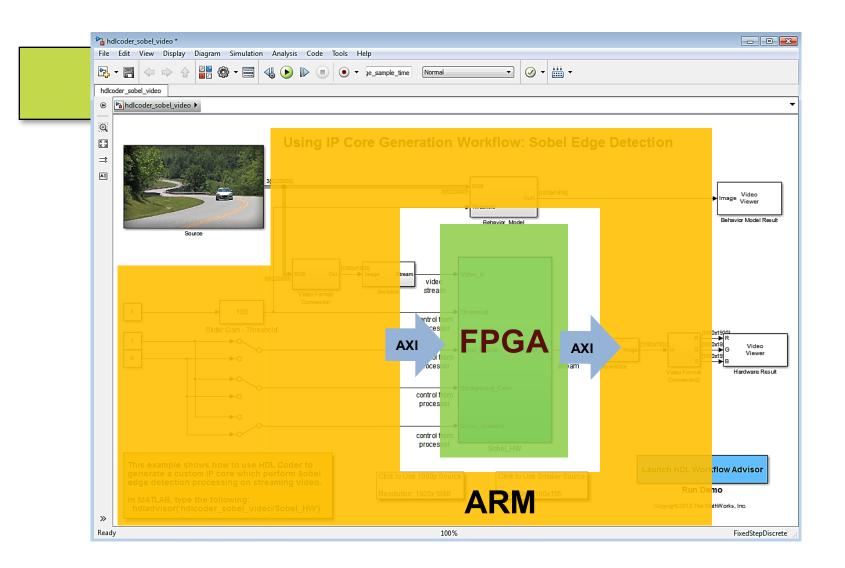

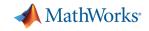

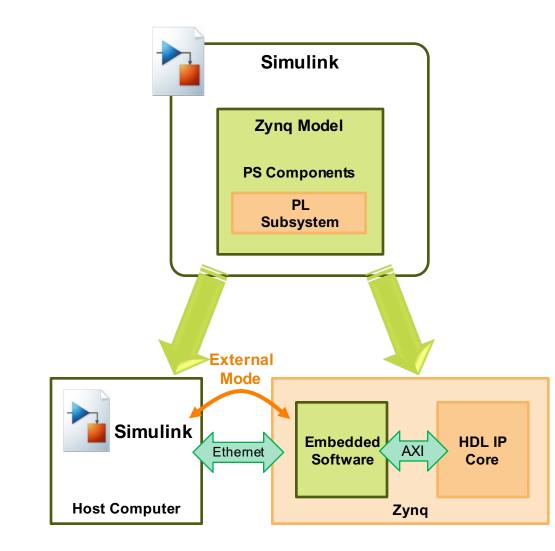

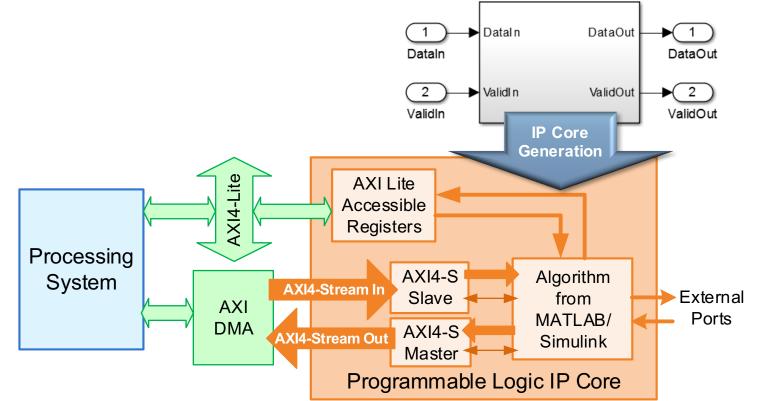

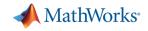

#### **Zynq Streaming Interface Support**

- Generate HDL IP core with AXI4-Stream interface

- Enable high speed data transfer

- Simplify streaming protocol

**R**2015b

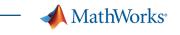

#### **AXI4-Stream Vector Mode**

- Modeling HW and SW together

- Automatic generation of SW DMA driver

- Focus on HW/SW Rapid Prototyping

#### Agenda

- Introduction

- What is Zynq?

- Design Challenges

- ZYNQ Design Process

- MBD on Programmable SoC

- Code Generation

- Workflow

- Verification & Partitioning

- Parameter Tuning

- UDP Interface

- Processor In the Loop

- Advanced Features

- Conclusions

#### **Conclusions: Design Concept Summary**

- Focus on algorithm and system design

- Stay on higher level of abstraction

- Automatic code generation and HW/SW integration

- Fast Prototyping and Easy integration with IDE

- Partitioning through Profiling

#### **Conclusions: Related Training Summary**

| Training Title                                | Details                                                        |  |  |

|-----------------------------------------------|----------------------------------------------------------------|--|--|

| Signal Processing with MATLAB                 | Signal Analysis and Algorithm Design (2 days)                  |  |  |

| Image Processing with MATLAB                  | Image Analysis and Processing (2 days)                         |  |  |

| Signal Processing with Simulink               | Signal Processing Based Modeling & Dynamic Simulation (3 days) |  |  |

| Communication System Modeling with Simulink   | Communication System Modeling & Simulation (1 day)             |  |  |

| Stateflow for Logic-Driven System<br>Modeling | Flow Chartand FSM Modeling (2 days)                            |  |  |

| Interfacing MATLAB with C                     | Interfacing MATLAB and C Code via APIs (1 days)                |  |  |

| MATLAB to C with MATLAB                       | using MATLAB Coder (2 days)                                    |  |  |

| Embedded Coder for Produc<br>Generation       | estions? stem from Simulink Model (3 days)                     |  |  |

| Generating HDL Code from Simulink             | HDL Code Generation & Verification (2 days)                    |  |  |

| Programming Zynq with MATLAB and Simulink     | HW/SW Co-design on Zynq (include ZedBoard) (2 days)            |  |  |

# **Thank You**