Simulink Design Verifier 는 정형 기법을 사용하여 모델에 숨겨진 설계 오류를 식별할 수 있습니다. 정수 오버플로, 데드 로직, 배열 액세스 위반, 0으로 나누기를 발생시키는 모델 내의 블록을 검출할 수 있습니다. 설계가 기능 요구사항을 충족하는지를 정형적으로 검증할 수 있습니다. 각 설계 오류 또는 요구사항 위반에 대해 디버그할 수 있도록 시뮬레이션 테스트 케이스를 생성할 수 있습니다.

Simulink Design Verifier는 모델 커버리지 및 사용자 지정 목표에 대한 테스트 케이스를 생성하여 기존의 요구사항 기반 테스트 케이스를 확장할 수 있습니다. 이러한 테스트 케이스를 통해 모델이 조건, 결정, MCDC(수정 조건/결정) 및 사용자 지정 커버리지 목표를 충족할 수 있습니다. 커버리지 목표뿐만 아니라 사용자 지정 테스트 목표를 지정하여 요구사항 기반 테스트 케이스를 자동으로 생성할 수도 있습니다.

IEC Certification Kit (for ISO 26262 and IEC 61508) 및 DO Qualification Kit (for DO-178 and DO-254)를 통해 산업 표준 지원이 가능합니다.

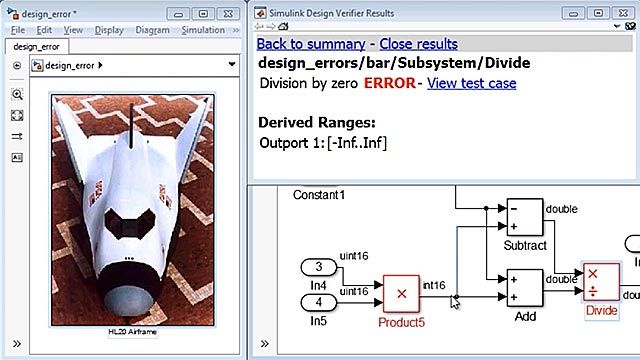

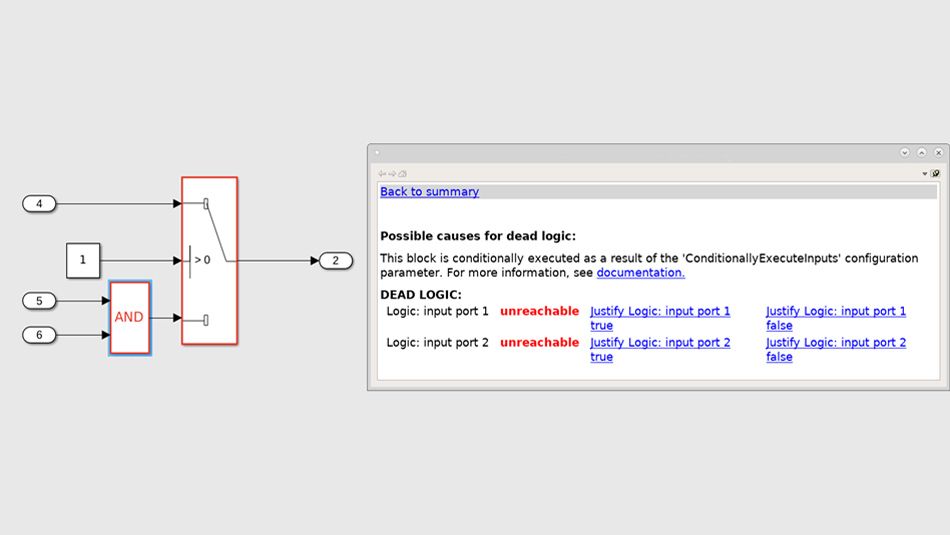

런타임 및 진단 오류 검출

시뮬레이션을 실행하기 전에 정수 오버플로, 0으로 나누기, 범위를 벗어난 배열, 준정규 값, 부동소수점 오류 및 데이터 유효성 오류 등의 런타임 및 모델링 오류를 검출할 수 있습니다.

누락된 테스트 커버리지 분석

수동으로 생성한 기존의 테스트 케이스를 증대 및 확장하여, Simulink 블록과 Stateflow 차트에서 호출된 C/C++ 코드나 생성된 코드의 커버리지와 불완전한 모델 커버리지를 해결할 수 있습니다.

정형 안전 요구사항 검증하기

MATLAB, Simulink 및 Stateflow를 사용하여 정형적으로 정의된 안전 요구사항에 따라 (3:53) 설계가 동작하는지 검증할 수 있습니다.

제품 관련 자료:

“모델 기반 설계를 통해 요구사항을 신속하게 분석하고 이전 제품의 설계를 재사용하고 수작업 코딩에 따른 오류를 없앨 수 있어 개발 시간을 단축하고 고객의 필요에 맞춰 일정을 단축할 수 있었습니다.”

MyoungSuk Ko, LS Automotive