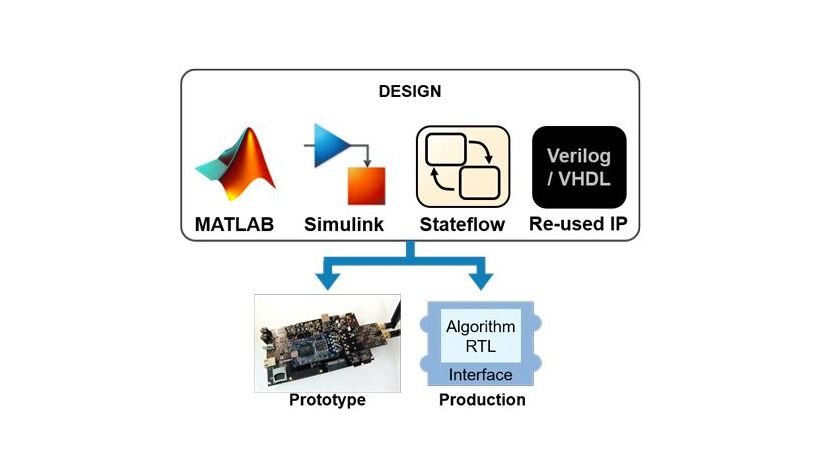

HDL Coder는 이식성이 좋고 합성 가능한 Verilog® 및 VHDL® 코드를 MATLAB 함수, Simulink 모델, Stateflow 차트로부터 생성하여 FPGA, SoC, ASIC에 대한 상위 수준 설계를 지원합니다. 사용자는 생성된 HDL 코드를 FPGA 프로그래밍, ASIC 프로토타이핑, 생산 설계에 활용할 수 있습니다.

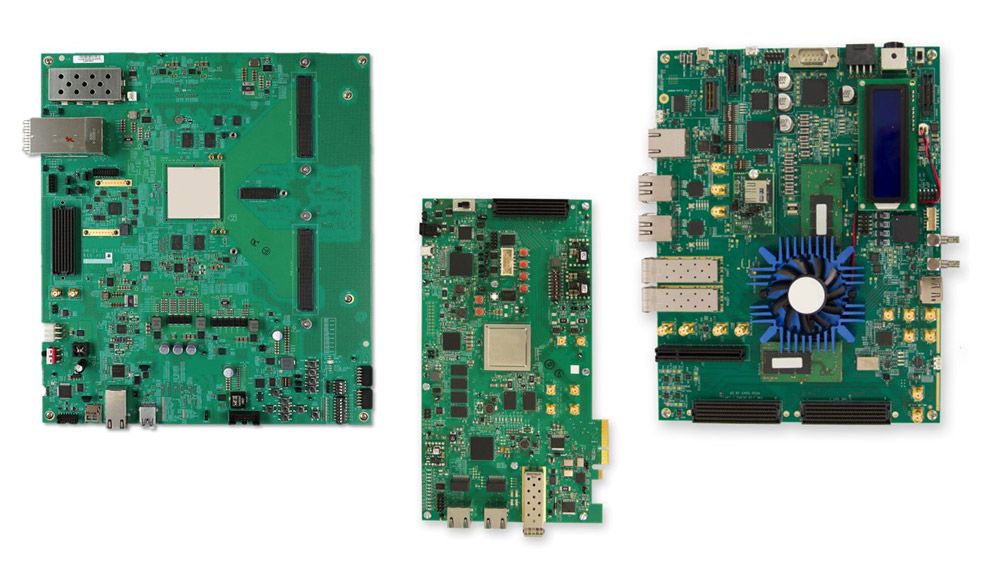

HDL Coder에는 AMD®, Intel®, Microchip 보드의 생성 코드 프로토타이핑을 자동화하고 IP 코어를 생성하여 ASIC 및 FPGA 워크플로를 지원하는 HDL Workflow Advisor가 있습니다. 사용자는 합성 전에 속도 및 면적에 대해 최적화를 수행하고, 임계 경로를 강조 표시하고, 리소스 활용 추정값을 생성할 수 있습니다. HDL Coder는 Simulink 모델과 생성된 Verilog 및 VHDL 코드 간의 추적성을 제공해 DO-254 및 기타 표준을 따르는 고무결성 응용 사례를 위한 코드 검증을 지원합니다.

상위 수준 하드웨어 설계

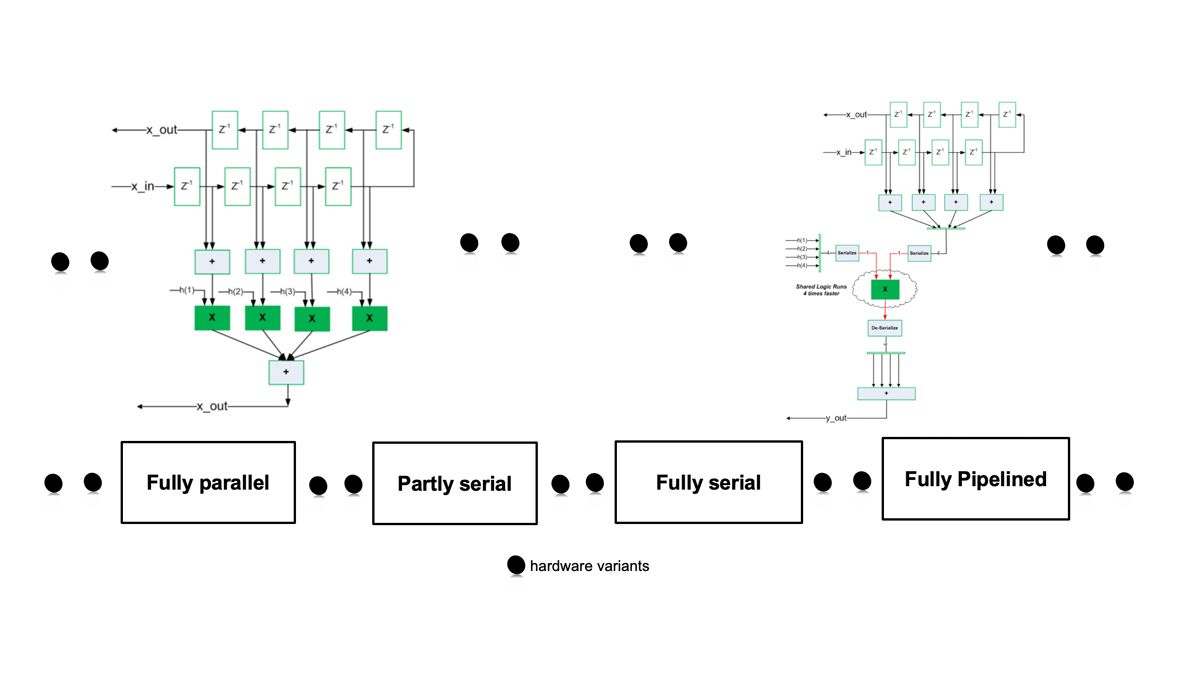

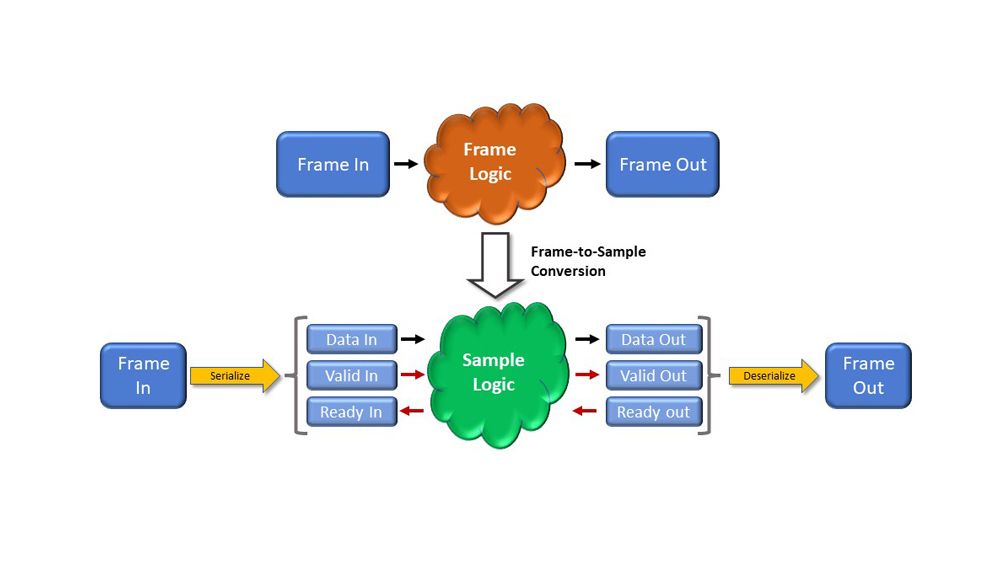

HDL과 호환되는 300개 이상의 Simulink 블록과 MATLAB 함수 중에서 선택하여 서브시스템을 설계하고 Stateflow 차트, Simscape 모델, 딥러닝 신경망을 추가할 수 있습니다. 설계의 하드웨어 동작을 시뮬레이션하고, 대안적인 아키텍처를 살펴보고, 고정소수점이나 부동소수점 데이터형, 또는 두 데이터형의 조합을 활용하여 합성 가능한 VHDL 또는 Verilog를 생성할 수 있습니다.

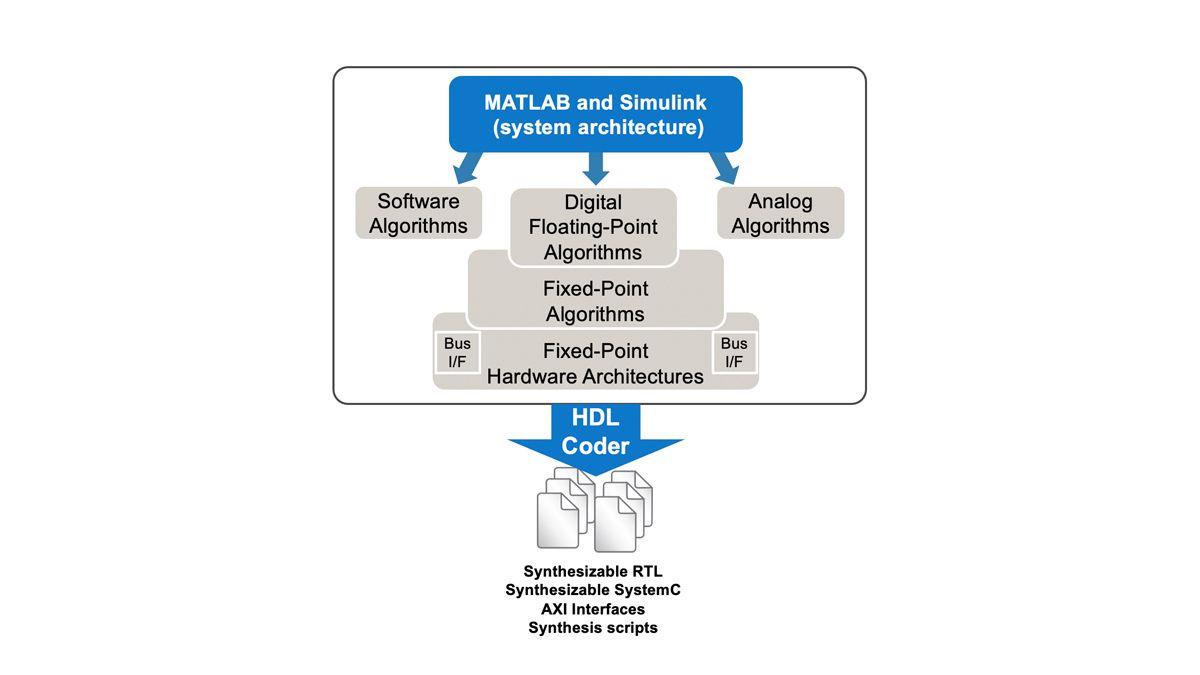

ASIC 워크플로

혼합 아날로그, 디지털 및 소프트웨어 시스템의 맥락에서 아키텍처와 상위 수준 하드웨어 기능을 설계하고 검증할 수 있습니다. QoR(결과 품질)이 우수한 RTL을 생성하거나 Cadence® Stratus HLS에서 사용할 합성 가능한 SystemC를 생성할 수 있습니다.

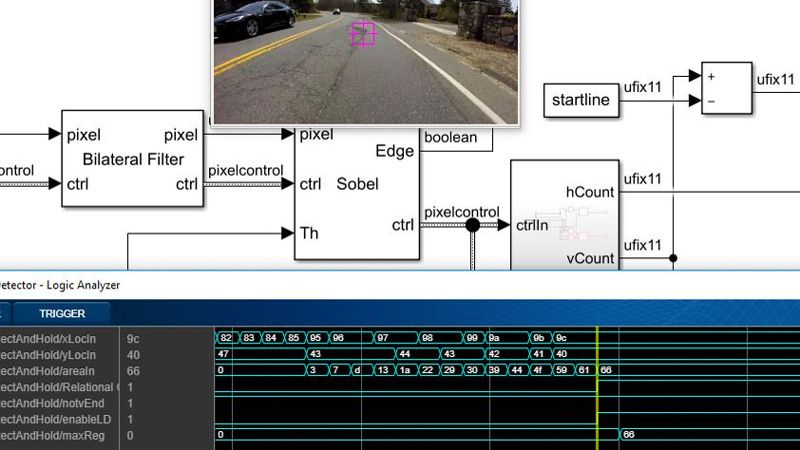

응용 사례 개발

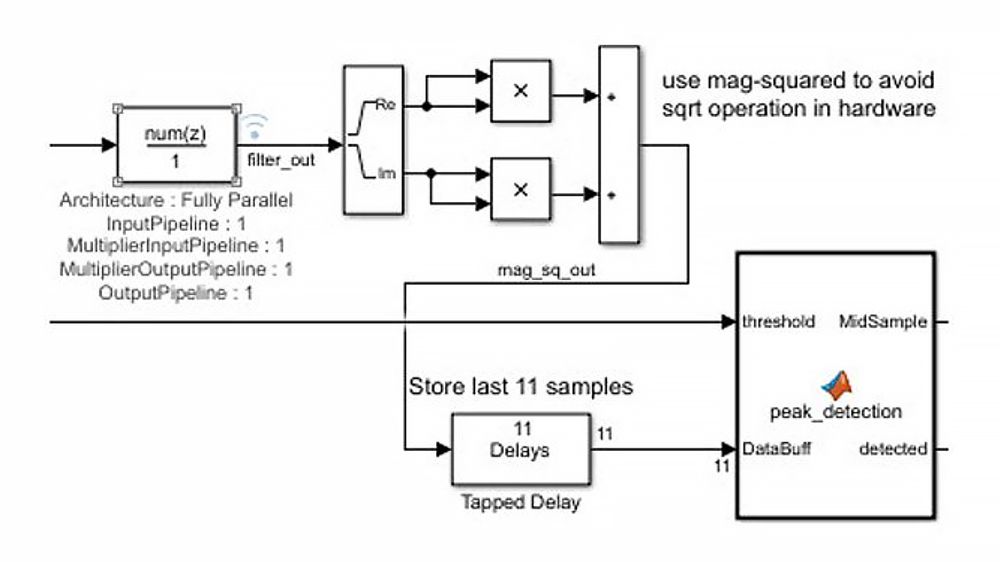

Wireless HDL Toolbox 의 서브시스템과 블록으로 통신 알고리즘을 설계하거나 Vision HDL Toolbox 를 사용하여 비전 처리 알고리즘의 스트리밍 구현을 개발할 수 있습니다. 복잡한 저지연 모터 제어 시스템을 구현할 수 있습니다.

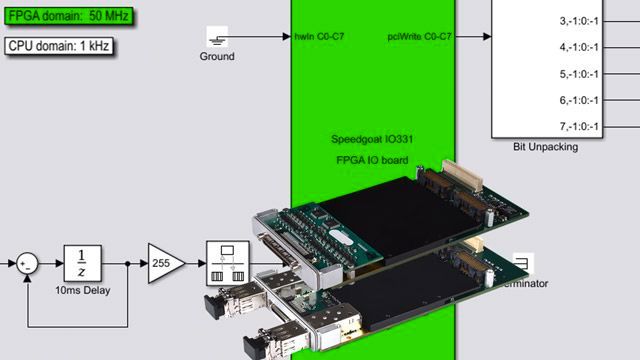

실시간 시뮬레이션 및 테스트

HDL Workflow Advisor을 사용하여 Speedgoat의 프로그램 가능 FPGA I/O 모듈을 타겟팅하고 Simulink Real-Time을 사용하여 시뮬레이션하거나 dSPACE 및 NI의 추가적인 FPGA I/O 모듈을 사용할 수 있습니다. 네이티브 부동소수점 HDL 코드를 생성하여 고정확도 프로토타이핑의 워크플로를 간소화할 수 있습니다.

조기 검증

HDL Verifier 와 함께 사용하여 생성된 RTL이 시스템 맥락의 필요에 따라 기능하도록 할 수 있습니다. 주요 HDL 시뮬레이터와의 연동 시뮬레이션을 사용하여 생성된 HDL을 MATLAB 및 Simulink 테스트벤치로 검증할 수 있습니다. FPGA-in-the-Loop 테스트를 사용하여 FPGA 개발 보드에서 설계 구현을 검증할 수 있습니다.

제품 관련 자료:

"시스템 아키텍트와 하드웨어 디자이너는 Simulink를 통해 소통할 수 있습니다. Simulink는 지식, 아이디어, 설계를 교환할 수 있는 공통의 언어와 같습니다. Simulink와 HDL Coder 덕분에 우리는 VHDL 구문이나 코딩 규칙을 검사하는 대신에 시뮬레이션을 통한 알고리즘 개발과 설계 고도화에 집중할 수 있습니다."

Marcel van Bakel, Philips Healthcare